Analog-to-Digital Conversion

Marcel J.M. Pelgrom

# Analog-to-Digital Conversion

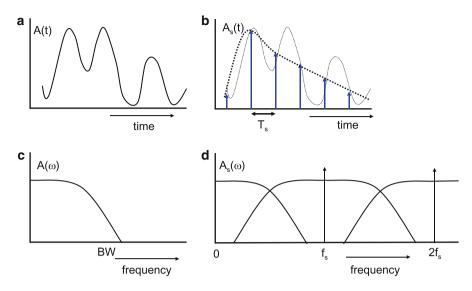

Second Edition

Marcel J.M.Pelgrom NXP Semiconductors Eindhoven Netherlands

ISBN 978-1-4614-1370-7 ISBN 978-1-4614-1371-4 (eBook) DOI 10.1007/978-1-4614-1371-4 Springer New York Heidelberg Dordrecht London

Library of Congress Control Number: 2012951650

#### © Springer Science+Business Media, LLC 2010, 2013

This work is subject to copyright. All rights are reserved by the Publisher, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, reuse of illustrations, recitation, broadcasting, reproduction on microfilms or in any other physical way, and transmission or information storage and retrieval, electronic adaptation, computer software, or by similar or dissimilar methodology now known or hereafter developed. Exempted from this legal reservation are brief excerpts in connection with reviews or scholarly analysis or material supplied specifically for the purpose of being entered and executed on a computer system, for exclusive use by the purchaser of the work. Duplication of this publication or parts thereof is permitted only under the provisions of the Copyright Law of the Publisher's location, in its current version, and permission for use must always be obtained from Springer. Permissions for use may be obtained through RightsLink at the Copyright Clearance Center. Violations are liable to prosecution under the respective Copyright Law.

The use of general descriptive names, registered names, trademarks, service marks, etc. in this publication does not imply, even in the absence of a specific statement, that such names are exempt from the relevant protective laws and regulations and therefore free for general use.

While the advice and information in this book are believed to be true and accurate at the date of publication, neither the authors nor the editors nor the publisher can accept any legal responsibility for any errors or omissions that may be made. The publisher makes no warranty, express or implied, with respect to the material contained herein.

Printed on acid-free paper

Springer is part of Springer Science+Business Media (www.springer.com)

### Preface

A book is like a window that allows you to look into the world. The window is shaped by the author and that makes that every window presents a unique view of the world. This is certainly true for this book. It is shaped by the topics and the projects throughout my career. Even more so, this book reflects my own style of working and thinking.

That starts already in Chap. 2. When I joined Philips Research in 1979, many of my colleagues used little paper notebooks to keep track of the most used equations and other practical things. This notebook was the beginning for Chap. 2: a collection of topics that form the basis for many of the other chapters. Chapter 2 is intended not to explain these topics but to refresh your knowledge and help you when you need some basics to solve more complex issues.

In the chapters discussing the fundamental processes of conversion, you will recognize my preoccupation with mathematics. I really enjoy finding an equation that properly describes the underlying mechanism. Nevertheless mathematics is not a goal on its own: equations help to understand the way how variables are connected to the result. Real insight comes from understanding the physics and electronics. In the chapters on circuit design I have tried to reduce the circuit diagrams to the simplest form, but not simpler. I do have private opinions on what works and what should not be applied. Most poor solutions have simply been left out; sometimes, you might read a warning in the text on a certain aspect of an interesting circuit.

Another of my favorites is the search for accuracy. In Chap. 11 you will find a detailed description, also in the earlier chapters, there is a lot of material referring to accuracy.

Circuit design and analog-to-digital circuit design is about bridging the gap between technology and systems. Both aspects have been treated less than they deserve. Still I hope it will be sufficient to create an interest to probe further.

This book is based on my lectures for graduate students who are novice in analogto-digital design. In the classes my aim is to bring the students to a level where they can read and interpret the literature (such as *IEEE Journal of Solid-State Circuits*) and judge the reported results on their merits. Still that leaves a knowledge gap with the designer of analog-to-digital converters. For those designers this book may serve as a reference of principles and background.

Inevitably this book has not only some strong points but also weak points. There are still so many wonderful ideas that are not addressed here but certainly would deserve some space and simply did not fit in this volume. Still I hope this book will let you experience the same thrill that all analog-to-digital designers feel, when they talk about their passion. Because that is the goal of this book: to encourage you to proceed on the route towards even better analog-to-digital converters.

Stiphout, the Netherlands, Christmas 2009

### **Second Edition**

In the second edition a number of errors have been corrected and a few topics have been updated. The most important change is the addition of many examples and exercises to assist students in understanding the material.

Stiphout, the Netherlands, Summer 2012

### Acknowledgements

Archimedes said: "Give me one fixed point and I will move the Earth." Home has always served for me as the fixed point from which I could move forward in my work. I owe my wife Elisabeth a debt of gratitude for creating a wonderful home. She herself was once part of this semiconductor world and understands its crazy habits. Yet, the encouragement and support she gave me is invaluable.

This book reflects parts of my 33 years of work in the Philips Natuurkundig Laboratorium and its successor. If there is anything I would call "luck" in my life, it was the opportunity to work in this place. The creativity, energy, opportunities, and people in this laboratory are unique. It is not trivial to create such research freedom in a financially driven industry. My 7 years as a mixed-signal department head have taught me that. Therefore I am truly grateful to those who served in the management of Philips Research and backed me when working on things outside the project scope or looking in unusual directions—just naming here: Theo van Kessel, Kees Wouda, Gerard Beenker, Hans Rijns, and Leo Warmerdam.

A laboratory is just as good as the people who work in it. In my career I met a lot of extraordinary people. They formed and shaped my way of thinking and analyzing problems. They challenged my ideas, took the time to listen to my reasoning, and pointed me in promising directions. I am grateful for being able to use the insights and results of the mixed-signal circuits and systems group. Without the useful discussions and critical comments of the members of this group this book would not exist. However, there are many more colleagues who have contributed in some form. Without the illusion of being complete, I want to express my gratitude for a pleasant collaboration with: Carel Dijkmans, Rudy van der Plassche, Eduard Stikvoort, Rob van der Grift, Arthur van Roermund, Erik van der Zwan, Peter Nuijten, Ed van Tuijl, Maarten Vertregt, Pieter Vorenkamp, Johan Verdaasdonk, Anton Welbers, Aad Duinmaijer, Jeannet van Rens, Klaas Bult, Govert Geelen, Stephane Barbu, Laurent Giry, Robert Meyer, Othmar Pfarkircher, Ray Speer, John Jennings, Bill Redman-White, Joost Briaire, Pieter van Beek, Raf Roovers, Lucien Breems, Robert van Veldhoven, Kathleen Philips, Bram Nauta, Hendrik van der Ploeg, Kostas Doris, Erwin Janssen, Robert Rutten, Violeta Petrescu, Harry Veendrick, Hans Tuinhout, Jan van der Linde, Peter van Leeuwen, and many others.

This book is based on the lectures in the Philips Center for Technical Training, at universities, and in the MEAD/EPFL courses. I want to thank Prof. Bram Nauta and Prof. Kofi Makinwa for giving me the opportunity to teach at the Universities of Twente and Delft, Prof. Bruce Wooley and Prof. Boris Murmann of Stanford University for their collaboration, and Prof. Gabor Temes and Dr. Vlado Valence for inviting me to lecture in the MEAD and EPFL courses.

A special word of thanks goes to all the students for their questions, remarks, and stimulating discussions.

## Contents

| 1 | Introduction |          |                                     | 1  |

|---|--------------|----------|-------------------------------------|----|

|   | 1.1          | About    | This Book                           | 3  |

| 2 | Com          | ponents  | and Definitions                     | 5  |

|   | 2.1          | Mathen   | natical Tools                       | 5  |

|   |              | 2.1.1    | Fourier Transform                   | 9  |

|   |              | 2.1.2    | Fourier Analysis                    | 11 |

|   |              | 2.1.3    | Distortion                          | 14 |

|   |              | 2.1.4    | Laplace Transform                   | 18 |

|   |              | 2.1.5    | Z-Transform                         | 21 |

|   |              | 2.1.6    | Statistics                          | 22 |

|   |              | 2.1.7    | Functions of Statistical Variables  | 28 |

|   | 2.2          | Resistiv | vity                                | 31 |

|   |              | 2.2.1    | Temperature                         | 33 |

|   |              | 2.2.2    | Voltage and Temperature Coefficient | 35 |

|   |              | 2.2.3    | Measuring Resistance                | 35 |

|   |              | 2.2.4    | Electromigration                    | 36 |

|   |              | 2.2.5    | Noise                               | 37 |

|   | 2.3          | Maxwe    | Il Equations                        | 40 |

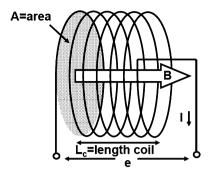

|   |              | 2.3.1    | Inductors                           | 43 |

|   |              | 2.3.2    | Energy in a Coil                    | 45 |

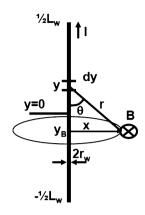

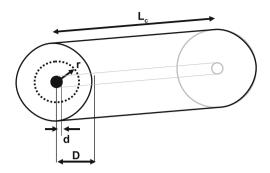

|   |              | 2.3.3    | Straight-Wire Inductance            | 45 |

|   |              | 2.3.4    | Skin Effect and Eddy Current        | 47 |

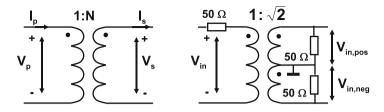

|   |              | 2.3.5    | Transformer                         | 47 |

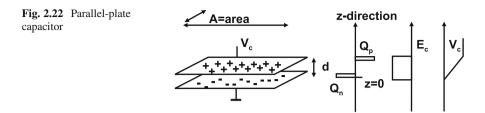

|   |              | 2.3.6    | Capacitors                          | 49 |

|   |              | 2.3.7    | Energy in Capacitors                | 50 |

|   |              | 2.3.8    | Partial Charging                    | 51 |

|   |              | 2.3.9    | Digital Power Consumption           | 52 |

|   |              | 2.3.10   | Coaxial Cable                       | 54 |

|   | 2.4          | Semico   | nductors                            | 56 |

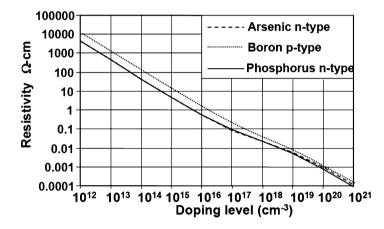

|   |              | 2.4.1    | Semiconductor Resistivity           | 57 |

|   |              |          |                                     |    |

|     | 2.4.2  | Voltage and Temperature Coefficient       | 58  |

|-----|--------|-------------------------------------------|-----|

|     | 2.4.3  | Matching of Resistors                     | 59  |

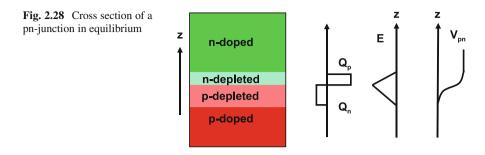

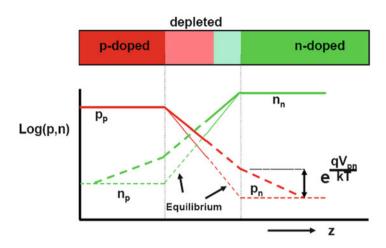

|     | 2.4.4  | pn-Junction                               | 59  |

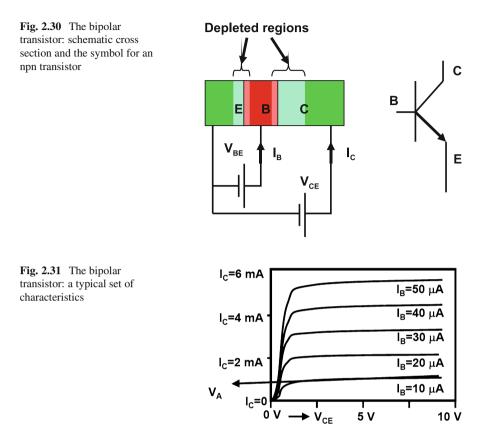

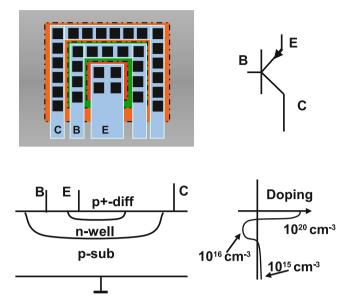

|     | 2.4.5  | Bipolar Transistor                        | 63  |

|     | 2.4.6  | Darlington Pair                           | 66  |

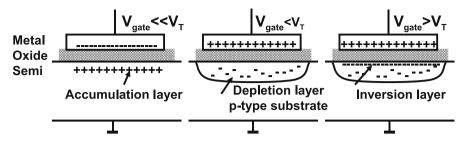

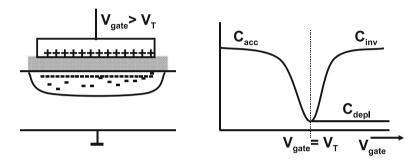

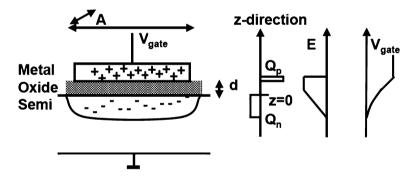

|     | 2.4.7  | MOS Capacitance                           | 66  |

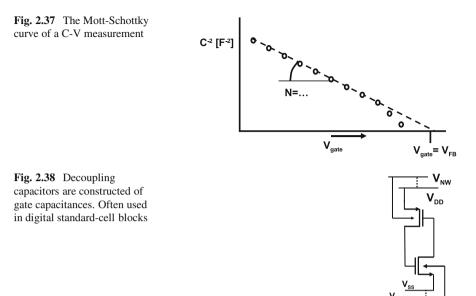

|     | 2.4.8  | Capacitance Between Layers                | 70  |

|     | 2.4.9  | Voltage and Temperature Coefficient       | 71  |

|     | 2.4.10 | Matching of Capacitors                    | 71  |

|     | 2.4.11 | Capacitor Design                          | 71  |

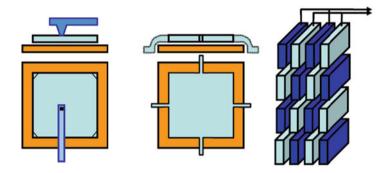

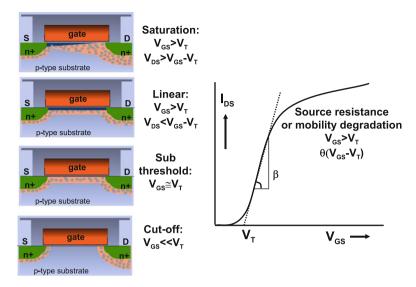

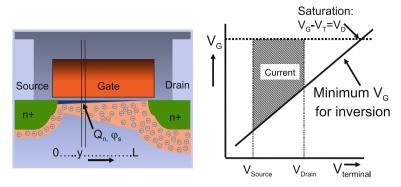

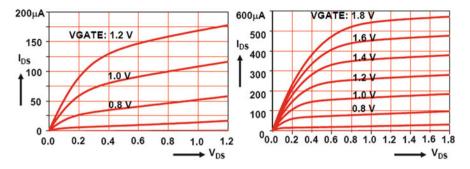

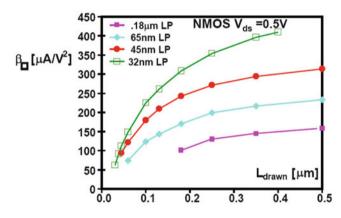

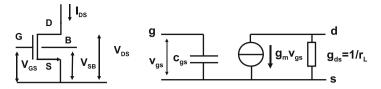

| 2.5 | MOS T  | ransistor                                 | 74  |

|     | 2.5.1  | Threshold Voltage                         | 78  |

|     | 2.5.2  | Weak Inversion                            | 80  |

|     | 2.5.3  | Large Signal and Small Signal             | 81  |

|     | 2.5.4  | Drain-Voltage Influence                   | 82  |

|     | 2.5.5  | Output Impedance                          | 83  |

|     | 2.5.6  | Matching                                  | 84  |

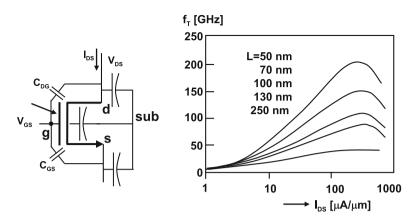

|     | 2.5.7  | High-Frequency Behavior                   | 86  |

|     | 2.5.8  | Gate Leakage                              | 87  |

|     | 2.5.9  | Temperature Coefficient                   | 88  |

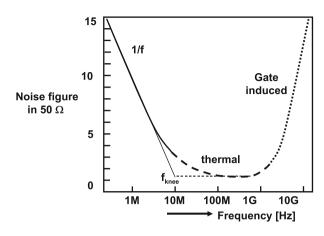

|     | 2.5.10 | Noise                                     | 89  |

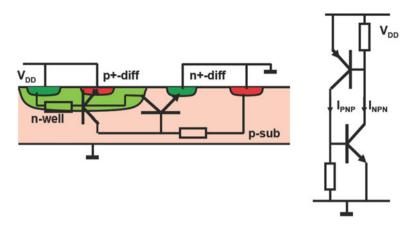

|     | 2.5.11 | Latch-Up                                  | 91  |

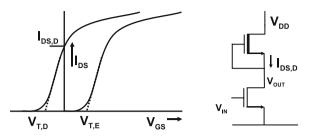

|     | 2.5.12 | Enhancement and Depletion                 | 92  |

|     | 2.5.13 | Models                                    | 93  |

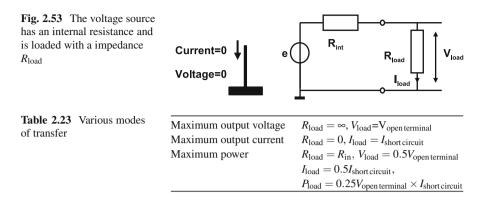

| 2.6 | Networ | k Theory                                  | 94  |

|     | 2.6.1  | Energy and Power                          | 94  |

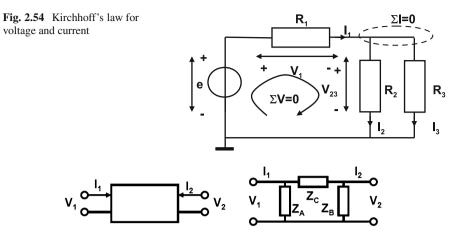

|     | 2.6.2  | Kirchhoff's Laws                          | 97  |

|     | 2.6.3  | Two-Port Networks                         | 97  |

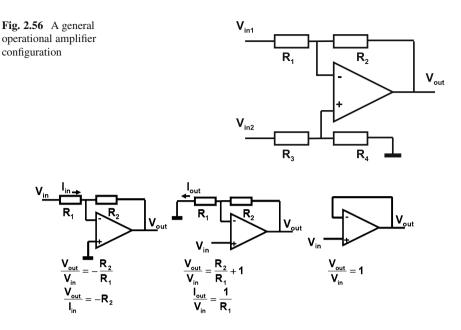

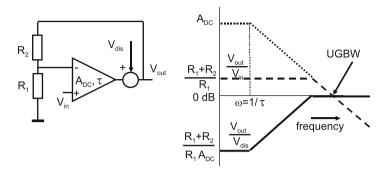

|     | 2.6.4  | Opamps and OTAs                           | 99  |

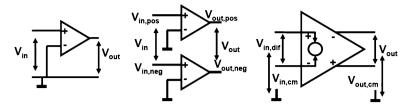

|     | 2.6.5  | Differential Design                       | 101 |

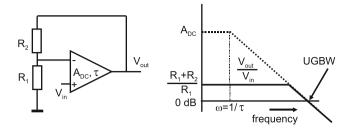

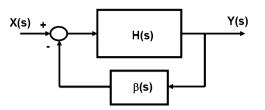

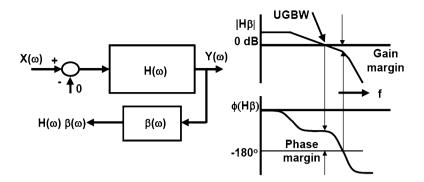

|     | 2.6.6  | Feedback                                  | 103 |

|     | 2.6.7  | Bode Plots                                | 106 |

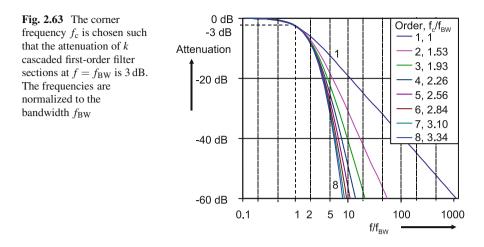

|     | 2.6.8  | Filters                                   | 107 |

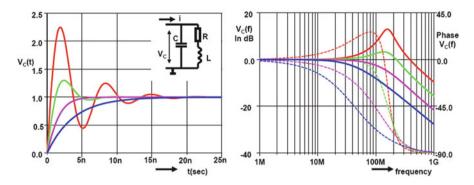

|     | 2.6.9  | RLC Filters                               | 110 |

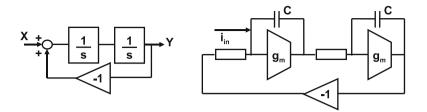

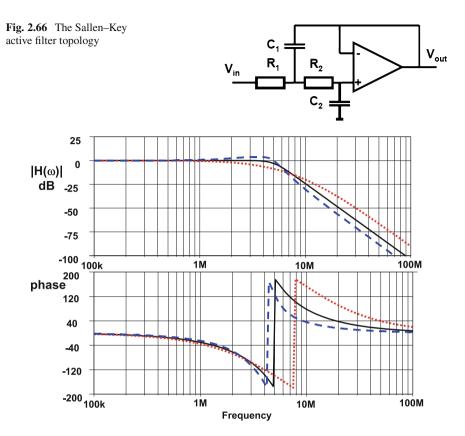

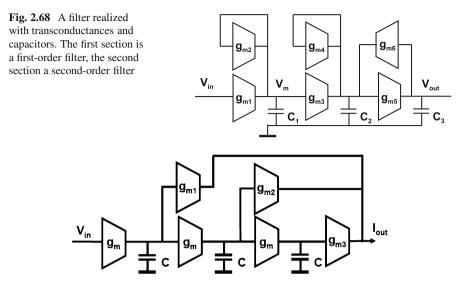

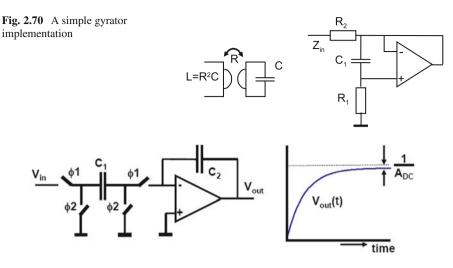

|     | 2.6.10 | Sallen–Key $g_m - C$ Filters and Gyrators | 113 |

|     | 2.6.11 | Switched-Capacitor Circuits               | 116 |

| 2.7 |        | nic Circuits                              | 119 |

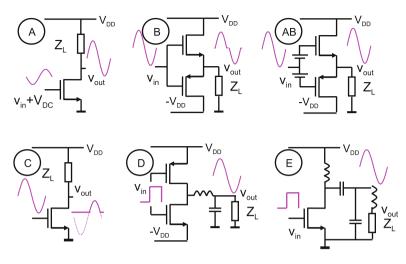

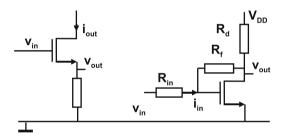

|     | 2.7.1  | Classification of Amplifiers              | 119 |

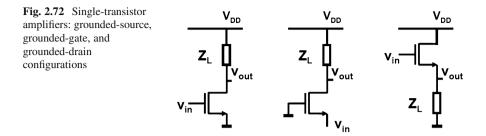

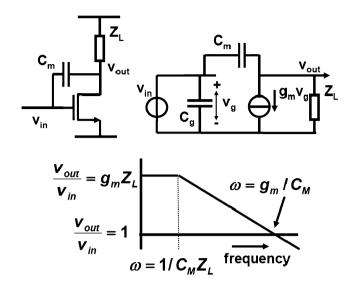

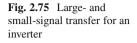

|     | 2.7.2  | One-Transistor Amplifier                  | 121 |

|     | 2.7.3  | Inverter                                  | 123 |

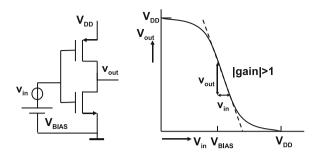

|     | 2.7.4  | Source Follower                           | 124 |

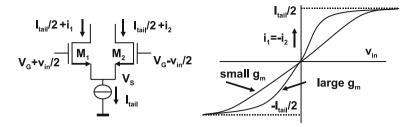

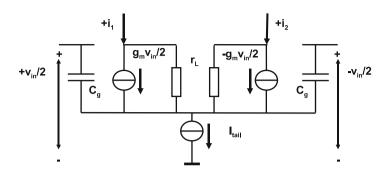

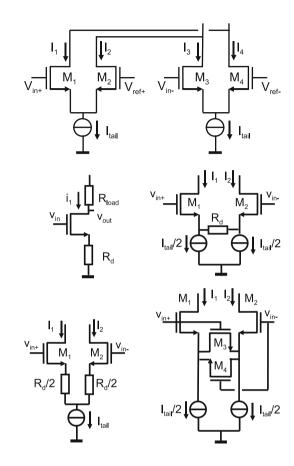

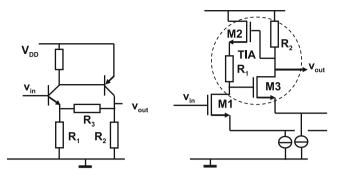

|     | 2.7.5  | Differential Pair                         | 125 |

|     | 2.7.6  | Degeneration                              | 129 |

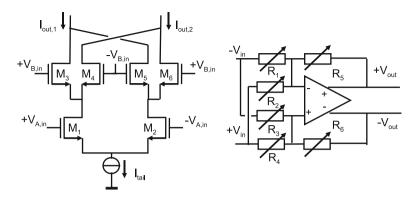

|     | 2.7.7  | Mixers and Variable Gain Amplifiers       | 130 |

|     | 2.7.8  | Current Mirror                            | 131 |

#### Contents

|   |                    | 2.7.9            | Cascode and Regulated Cascode             | 133        |

|---|--------------------|------------------|-------------------------------------------|------------|

|   |                    | 2.7.10           | Single-Stage Amplifier                    | 137        |

|   |                    | 2.7.11           | Miller Amplifier                          | 140        |

|   |                    | 2.7.12           | Choosing the W/L Ratios in a Miller Opamp | 143        |

|   |                    | 2.7.13           | Dominant-Pole Amplifier                   | 146        |

|   |                    | 2.7.14           | Feedback in Electronic Circuits           | 146        |

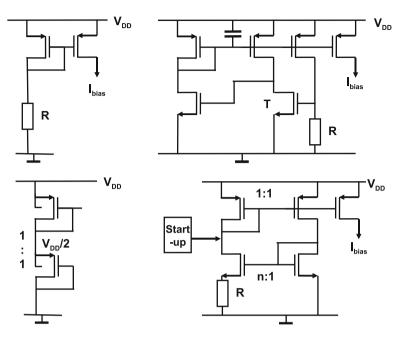

|   |                    | 2.7.15           | Bias Circuits                             | 148        |

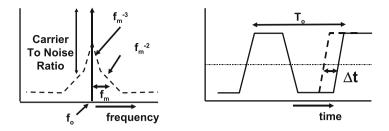

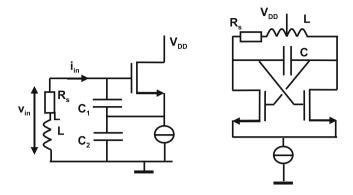

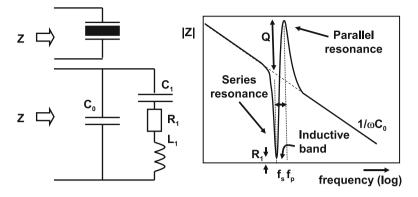

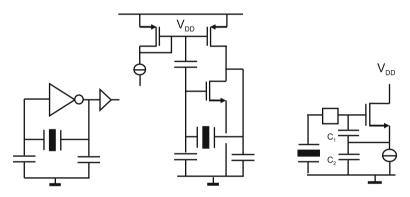

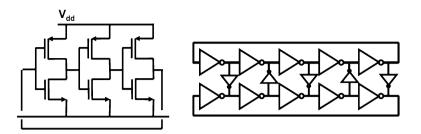

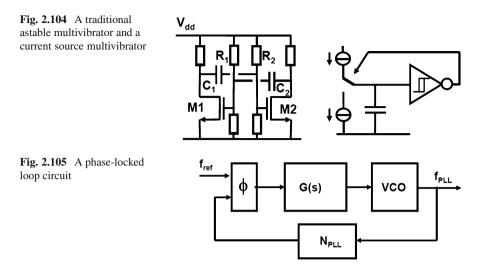

|   |                    | 2.7.16           | Oscillators                               | 150        |

| 3 | Samr               | ling             |                                           | 163        |

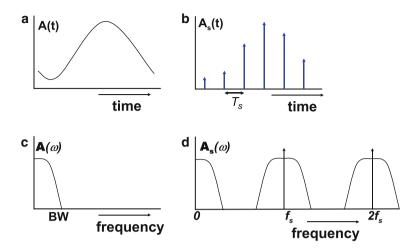

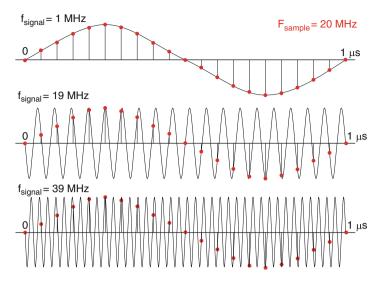

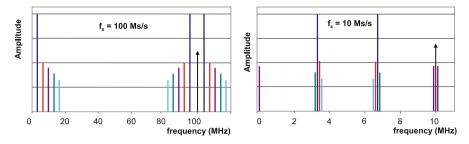

| 5 | 3.1                | <u> </u>         | ng in Time and Frequency                  | 163        |

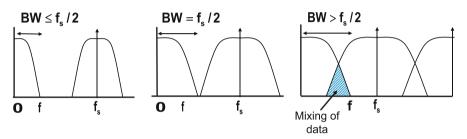

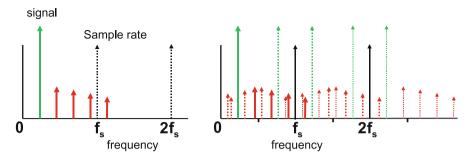

|   | 5.1                | 3.1.1            | Aliasing                                  | 168        |

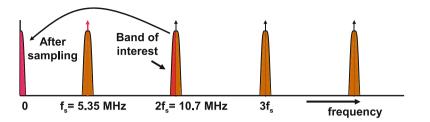

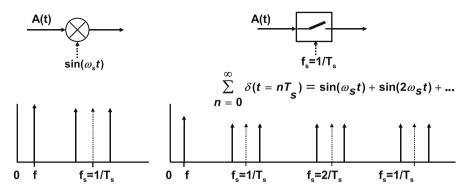

|   |                    | 3.1.2            | SubSampling                               | 169        |

|   |                    | 3.1.2            | Sampling, Modulation and Chopping         | 170        |

|   |                    | 3.1.4            | Nyquist Criterion                         | 173        |

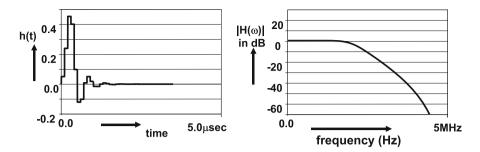

|   |                    | 3.1.5            | Alias Filter                              | 175        |

|   |                    | 3.1.6            | Sampling of Noise                         | 176        |

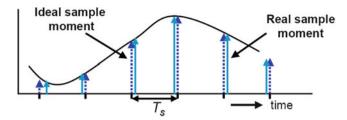

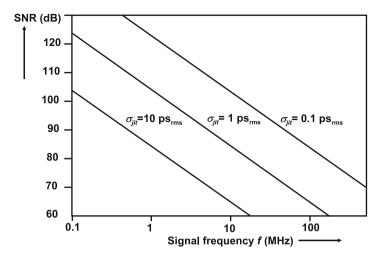

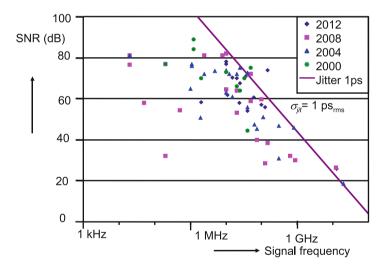

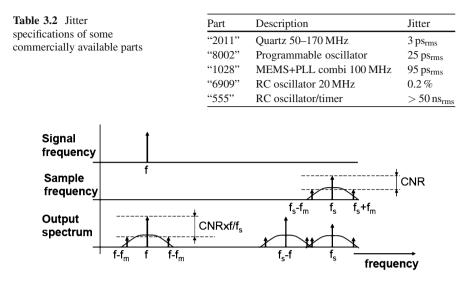

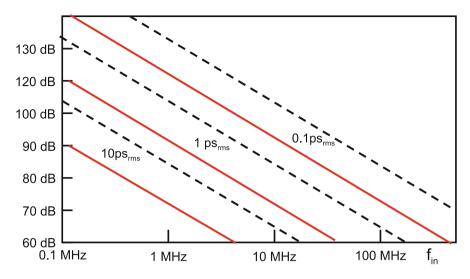

|   |                    | 3.1.7            | Jitter of the Sampling Pulse              | 179        |

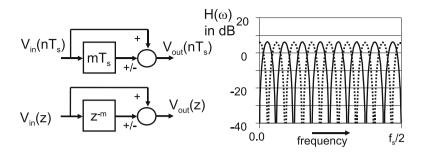

|   | 3.2                |                  | Discrete Filtering                        | 184        |

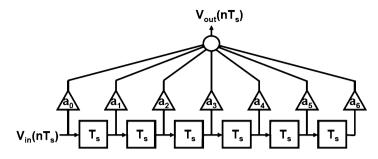

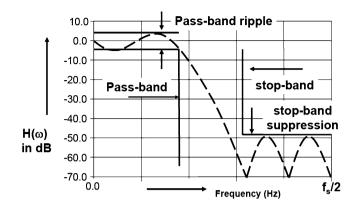

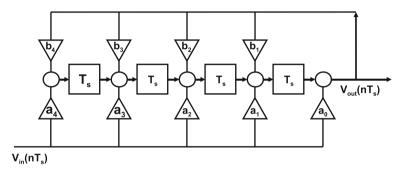

|   | 5.2                | 3.2.1            | FIR Filters                               | 184        |

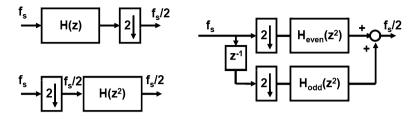

|   |                    | 3.2.2            | Half-Band Filters                         | 190        |

|   |                    | 3.2.3            | Down Sample Filter                        | 190        |

|   |                    | 3.2.4            | IIR Filters                               | 192        |

| 4 | Some               | lo and l         |                                           | 197        |

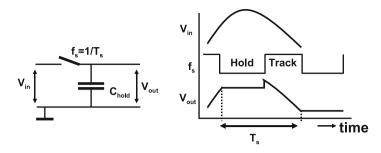

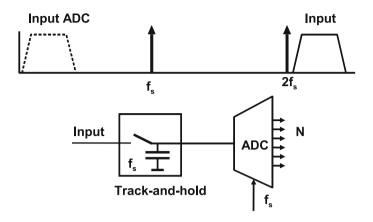

| 4 | <b>Samp</b><br>4.1 |                  | Hold                                      | 197        |

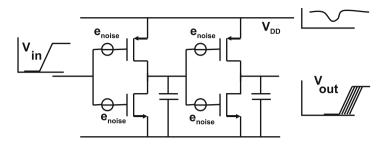

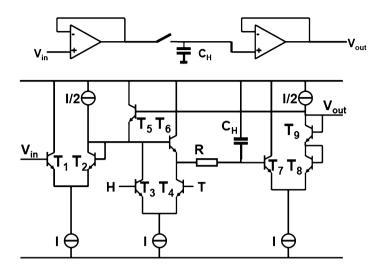

|   | 4.1                |                  | and-Hold and Sample-and-Hold Circuits     | 201        |

|   | 4.2                |                  |                                           | 201        |

|   | 4.5                | 4.3.1            | for and Switch Implementations            | 204<br>204 |

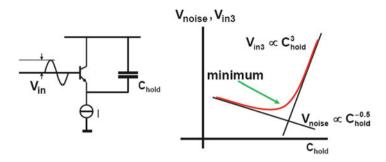

|   |                    | 4.3.1            | Capacitor                                 | 204        |

|   |                    | 4.3.2            | Switch Topologies                         |            |

|   |                    |                  | Bottom Plate Sampling                     | 209<br>210 |

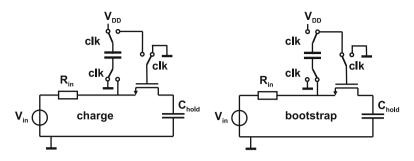

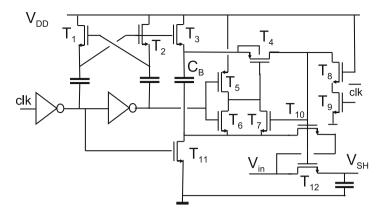

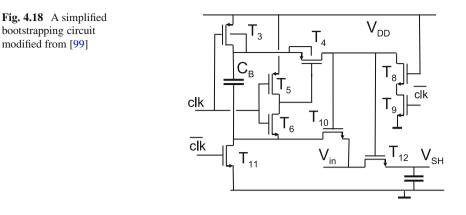

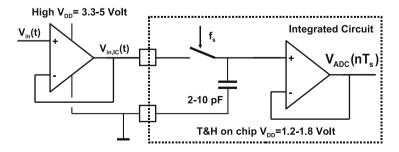

|   |                    | 4.3.4<br>4.3.5   | CMOS Bootstrap Techniques                 | 210        |

|   | 4.4                |                  | Buffering the Hold Capacitor              | 212        |

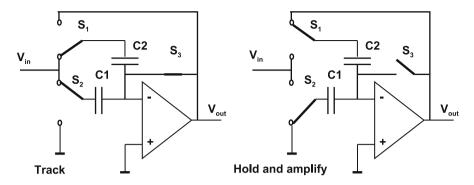

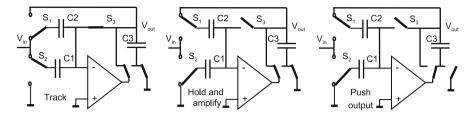

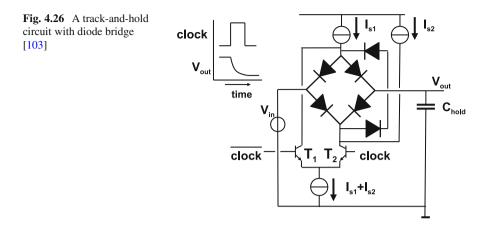

|   | 4.4                | 1таск-а<br>4.4.1 | nd-Hold Circuit Topologies                | 214        |

|   |                    | 4.4.1            | Basic Configurations                      | 214        |

|   |                    |                  | Amplifying Track-and-Hold Circuit         |            |

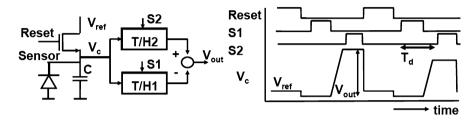

|   |                    | 4.4.3            | Correlated Double Sampling                | 219        |

|   |                    | 4.4.4            | Bipolar Examples                          | 220        |

|   |                    | 4.4.5            | Distortion and Noise                      | 222        |

| 5 | -                  |                  |                                           | 227        |

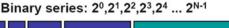

|   | 5.1                |                  | ty                                        | 229        |

|   |                    | 5.1.1            | Integral Linearity                        | 229        |

|   |                    | 5.1.2            | Differential Linearity                    | 231        |

|   |                    |                  |                                           |            |

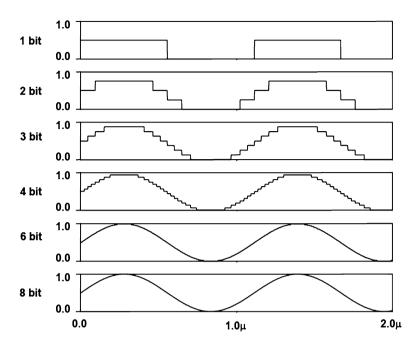

|   | 5.2                |                  | Cation Error                              | 234<br>234 |

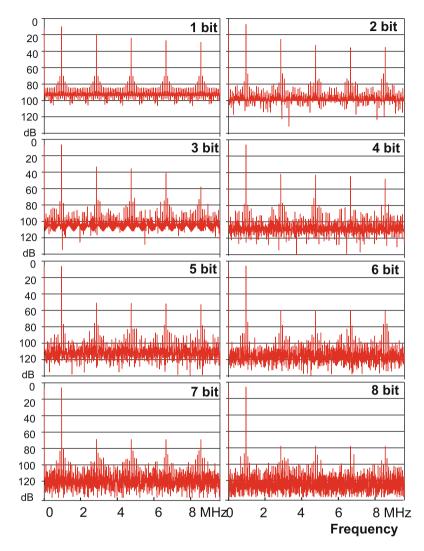

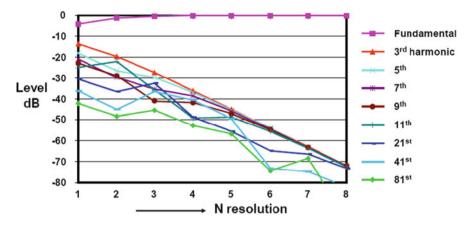

|   |       | 5.2.2     | 2–6 Bit Quantization                         | 234 |

|---|-------|-----------|----------------------------------------------|-----|

|   |       | 5.2.3     | 7-Bit and Higher Quantization                | 236 |

|   | 5.3   | Signal    | -to-Noise                                    | 238 |

|   |       | 5.3.1     | Related Definitions                          | 240 |

|   |       | 5.3.2     | Nonuniform Quantization                      | 242 |

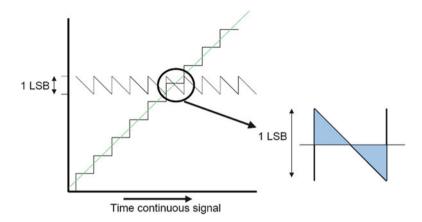

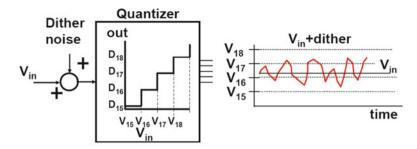

|   |       | 5.3.3     | Dither                                       | 242 |

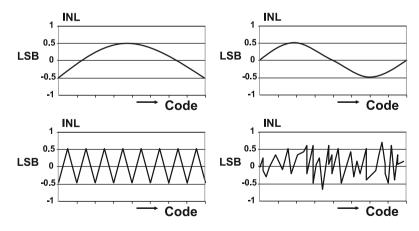

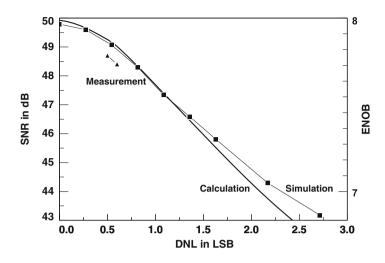

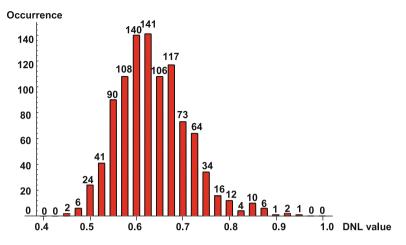

|   | 5.4   | Model     | ing INL and DNL                              | 244 |

| 6 | Refe  |           | ircuits                                      |     |

|   | 6.1   |           | al Requirements                              |     |

|   | 6.2   |           | ap Reference Circuits                        |     |

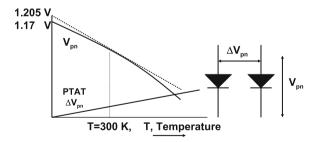

|   |       | 6.2.1     | Bandgap Principle                            |     |

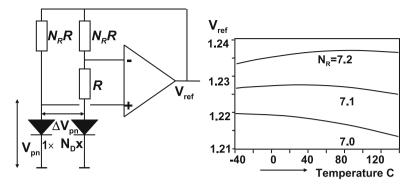

|   |       | 6.2.2     | Artifacts of the Standard Circuit            |     |

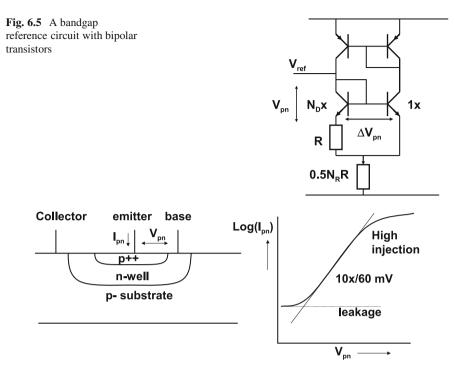

|   |       | 6.2.3     | Bipolar Bandgap Circuit                      |     |

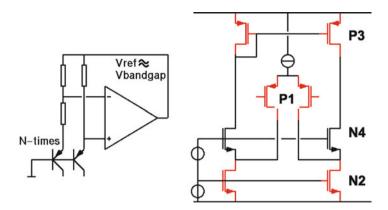

|   |       | 6.2.4     | CMOS Bandgap Circuit                         |     |

|   |       | 6.2.5     | Low-Voltage Bandgap Circuits                 |     |

|   | 6.3   | Altern    | ative References                             | 261 |

| 7 | Digit | tal-to-Ai | nalog Conversion                             | 265 |

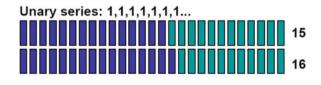

|   | 7.1   | Unary     | and Binary Representation                    | 266 |

|   |       | 7.1.1     | Digital Representation                       | 269 |

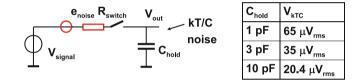

|   |       | 7.1.2     | Physical Domain                              | 270 |

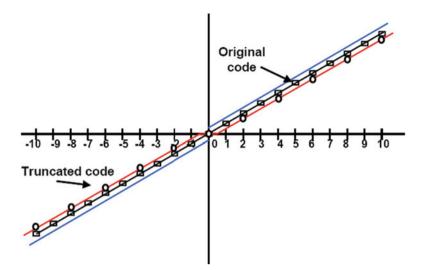

|   | 7.2   | Digital   | I-to-Analog Conversion in the Voltage Domain | 271 |

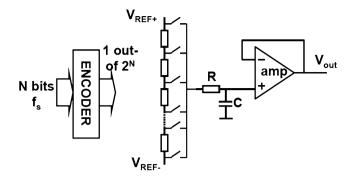

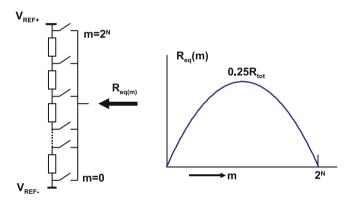

|   |       | 7.2.1     | Resistor Strings                             | 271 |

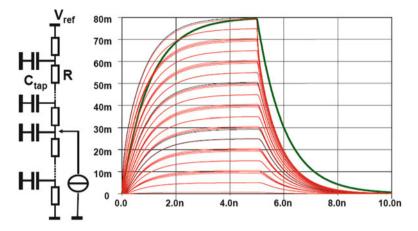

|   |       | 7.2.2     | Dynamic Behavior of the Resistor Ladder      | 273 |

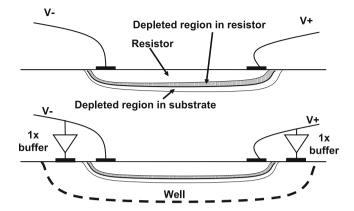

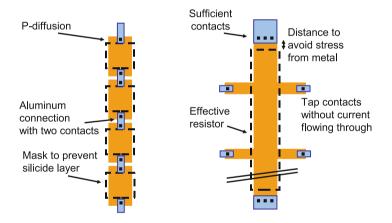

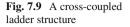

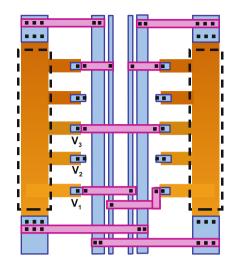

|   |       | 7.2.3     | Practical Issues in Resistor Ladders         |     |

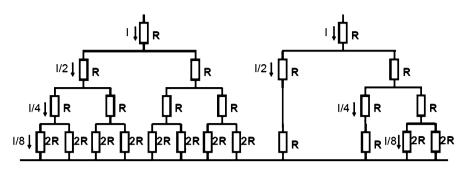

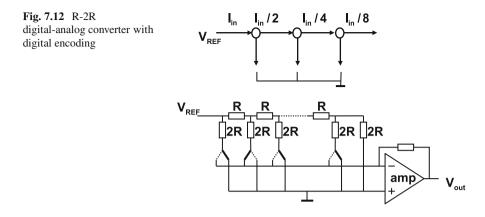

|   |       | 7.2.4     | R-2R Ladders                                 | 278 |

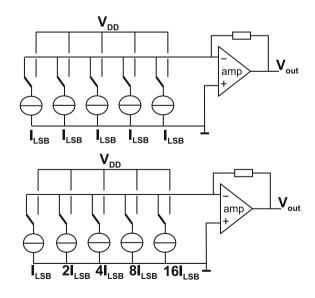

|   | 7.3   |           | I-to-Analog Conversion in the Current Domain | 281 |

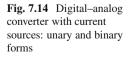

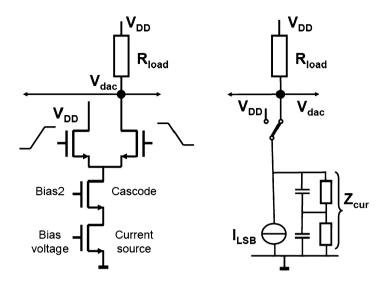

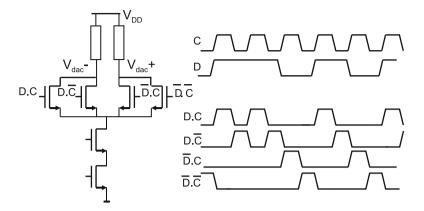

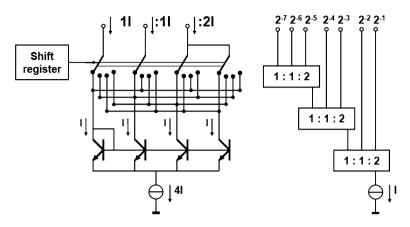

|   |       | 7.3.1     | Current Steering Digital-to-Analog Converter | 281 |

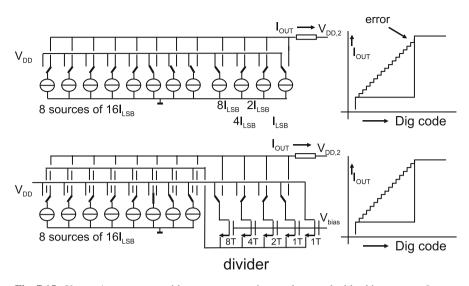

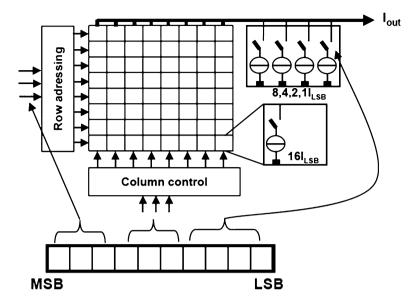

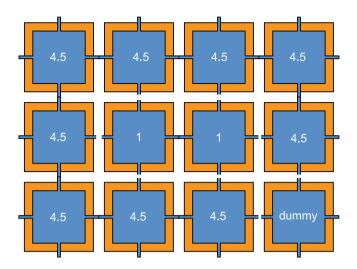

|   |       | 7.3.2     | Matrix Decoding                              | 283 |

|   |       | 7.3.3     | Current Cell                                 | 285 |

|   |       | 7.3.4     | Performance Limits                           |     |

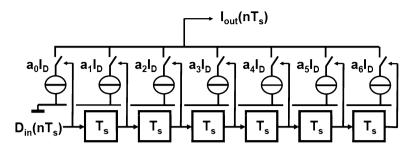

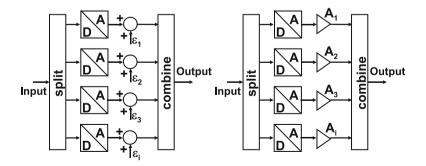

|   |       | 7.3.5     | Semi-digital Filter/Converters               |     |

|   | 7.4   | -         | I-to-Analog Conversion in the Charge Domain  |     |

|   | 7.5   | -         | I-to-Analog Conversion in the Time Domain    |     |

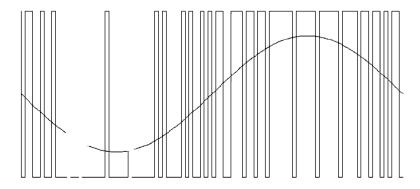

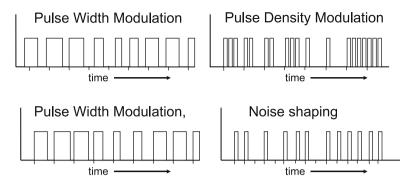

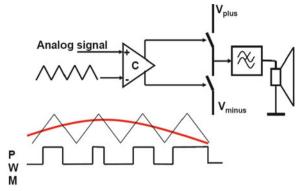

|   |       | 7.5.1     | Class-D Amplifiers                           |     |

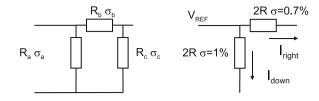

|   | 7.6   | Accura    | acy                                          |     |

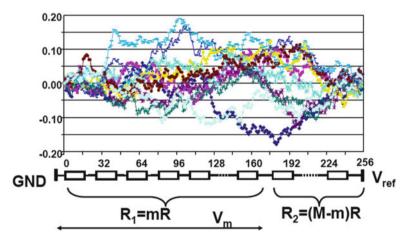

|   |       | 7.6.1     | Accuracy in Resistors Strings                |     |

|   |       |           | Accuracy in Current Source Arrays            |     |

|   | 7.7   |           | ds to Improve Accuracy                       |     |

|   |       | 7.7.1     | Current Calibration                          |     |

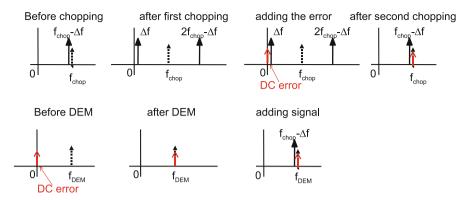

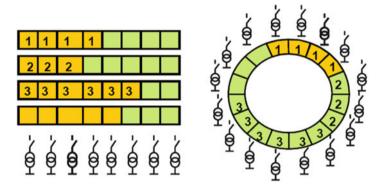

|   |       | 7.7.2     | Dynamic Element Matching                     |     |

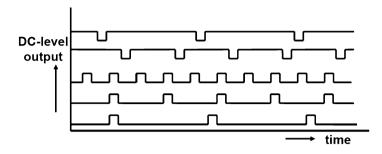

|   |       | 7.7.3     | Data-Weighted Averaging                      |     |

|   | 7.8   | -         | nentation Examples                           |     |

|   |       | 7.8.1     | Resistor-Ladder Digital-to-Analog Converter  |     |

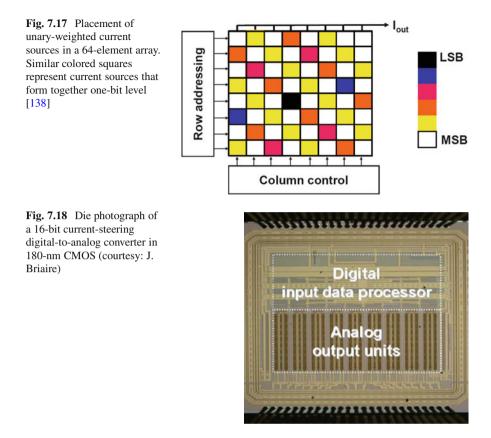

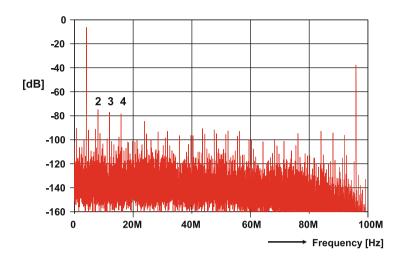

|   |       | 7.8.2     | Current-Domain Digital-to-Analog Conversion  | 316 |

|   |      | 7.8.3    | Comparison                                            | 318 |

|---|------|----------|-------------------------------------------------------|-----|

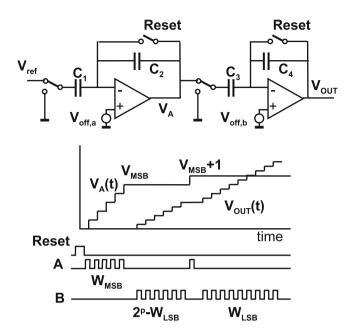

|   |      | 7.8.4    | Algorithmic Charge-Based Digital-to-Analog Converter. | 319 |

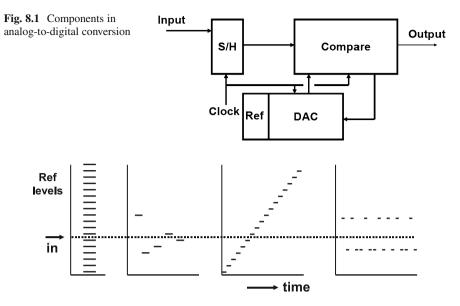

| 8 | Anal | og-to-Di | gital Conversion                                      | 325 |

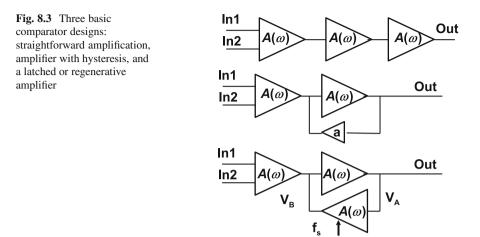

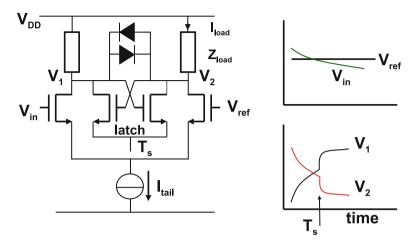

|   | 8.1  | Compa    | rator                                                 | 327 |

|   |      | 8.1.1    | Dynamic Behavior of the Comparator                    | 330 |

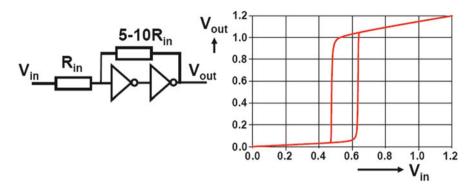

|   |      | 8.1.2    | Hysteresis                                            | 331 |

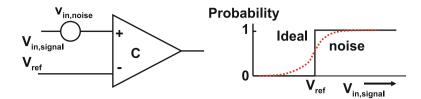

|   |      | 8.1.3    | Accuracy                                              | 333 |

|   |      | 8.1.4    | Metastability and Bit Error Rate                      | 335 |

|   |      | 8.1.5    | Kickback                                              | 336 |

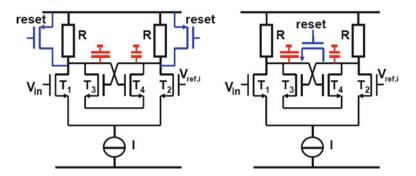

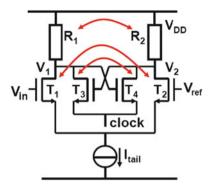

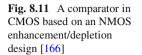

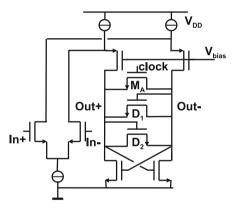

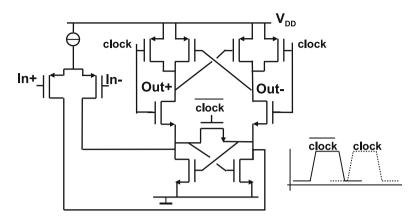

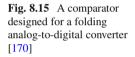

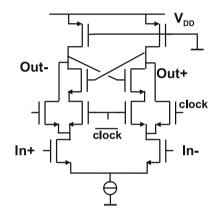

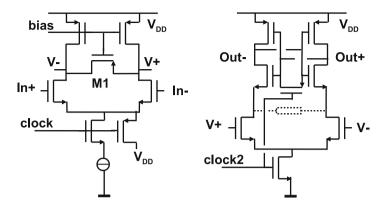

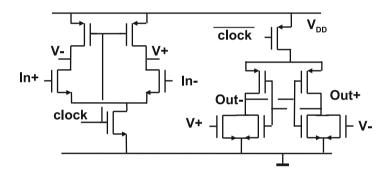

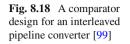

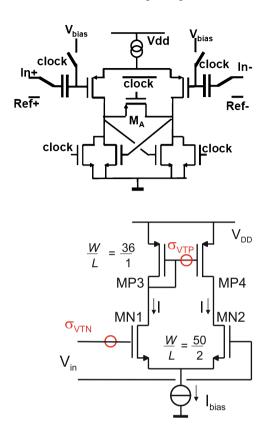

|   |      | 8.1.6    | Comparator Schematics                                 | 338 |

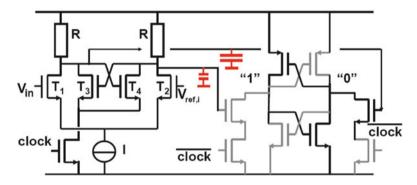

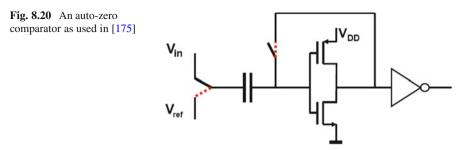

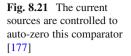

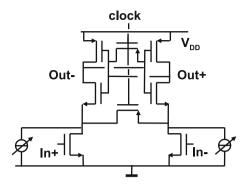

|   |      | 8.1.7    | Auto-Zero Comparators                                 | 343 |

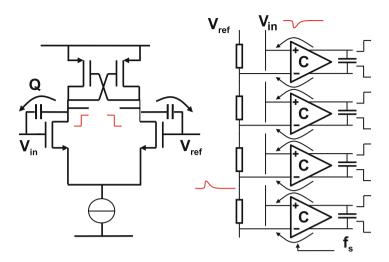

|   |      | 8.1.8    | Track-and-Hold Plus Comparator                        | 344 |

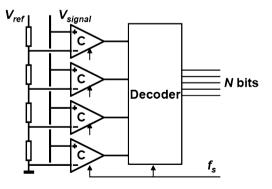

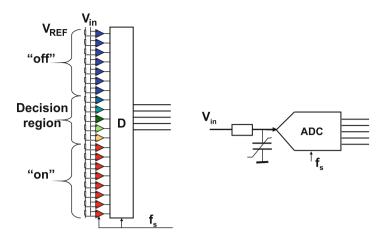

|   | 8.2  | Full-Fla | ash Converters                                        | 346 |

|   |      | 8.2.1    | Ladder Implementation                                 | 349 |

|   |      | 8.2.2    | Comparator Yield                                      | 350 |

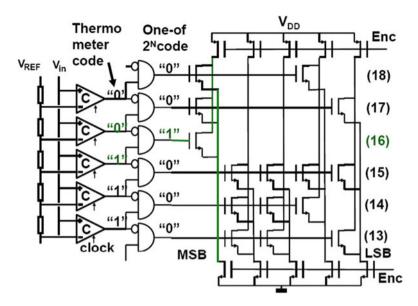

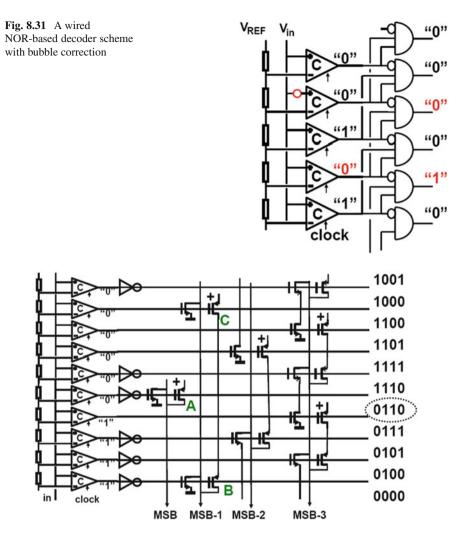

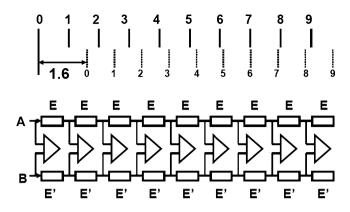

|   |      | 8.2.3    | Decoder                                               | 356 |

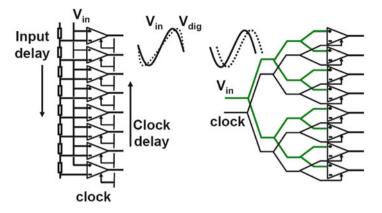

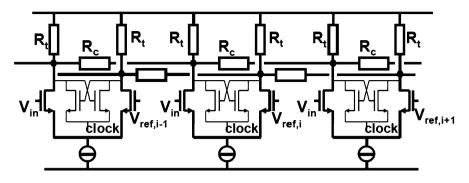

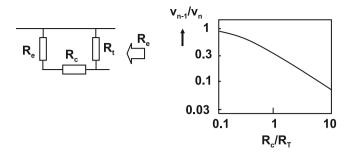

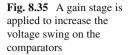

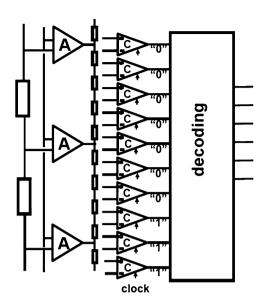

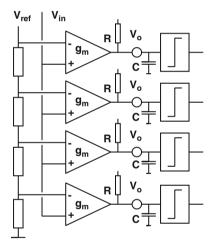

|   |      | 8.2.4    | Averaging and Interpolation                           | 358 |

|   |      | 8.2.5    | Frequency-Dependent Mismatch                          | 360 |

|   |      | 8.2.6    | Technology Scaling for Full-Flash Converters          | 362 |

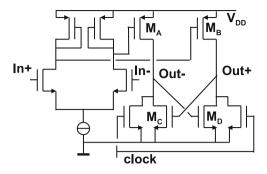

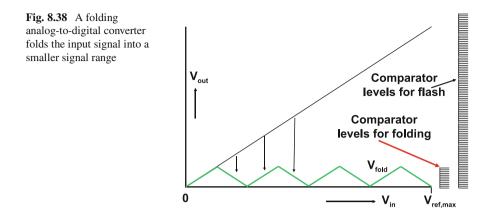

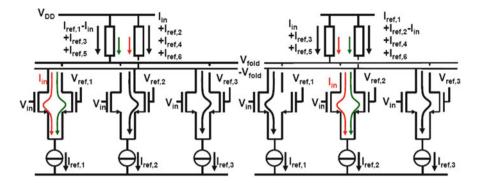

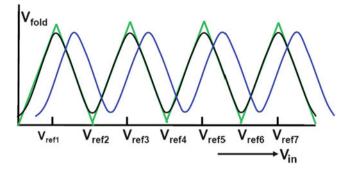

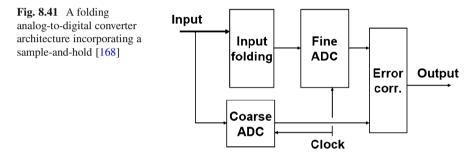

|   |      | 8.2.7    | Folding Converter                                     | 362 |

|   |      | 8.2.8    | Digital Output Power                                  | 365 |

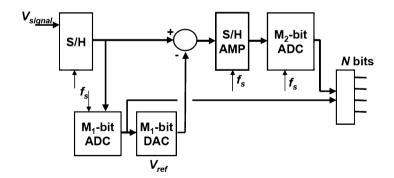

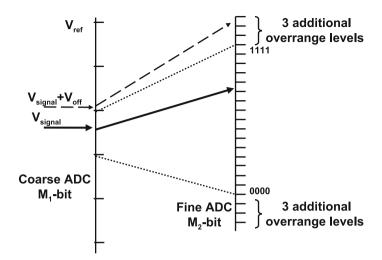

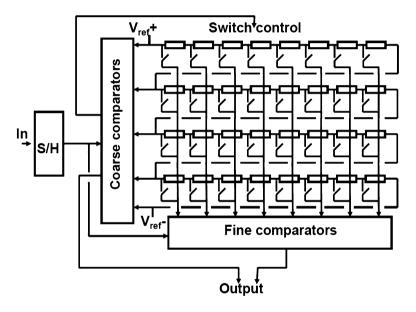

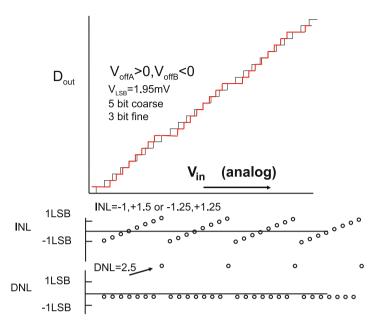

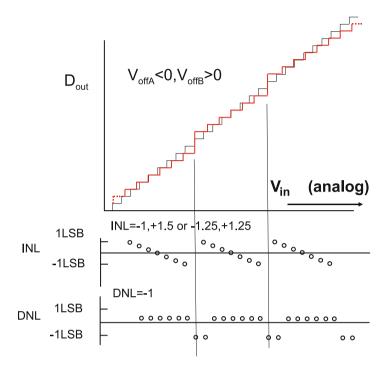

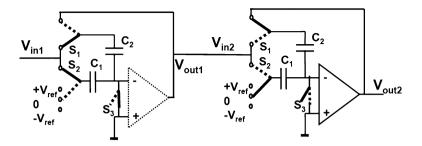

|   | 8.3  | Subran   | ging Methods                                          | 366 |

|   |      | 8.3.1    | Overrange                                             | 367 |

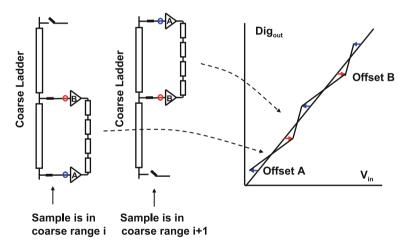

|   |      | 8.3.2    | Monkey Switching                                      | 368 |

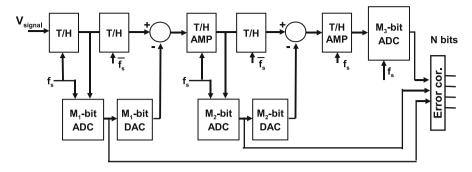

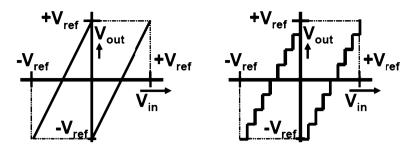

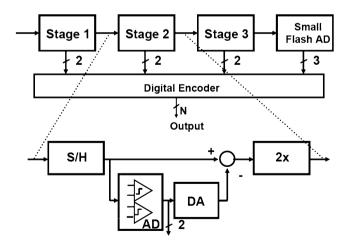

|   | 8.4  | 1-Bit P  | ipeline Analog-to-Digital Converters                  | 372 |

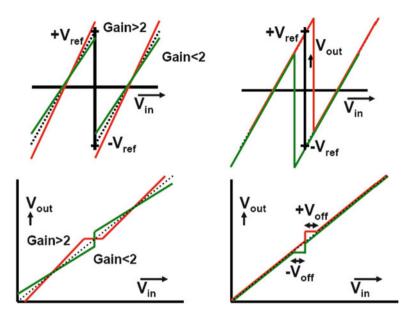

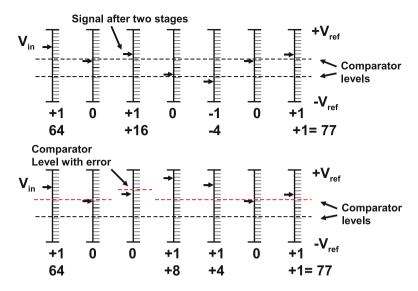

|   |      | 8.4.1    | Error Sources in Pipeline Converters                  | 376 |

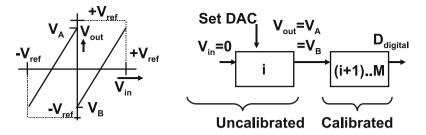

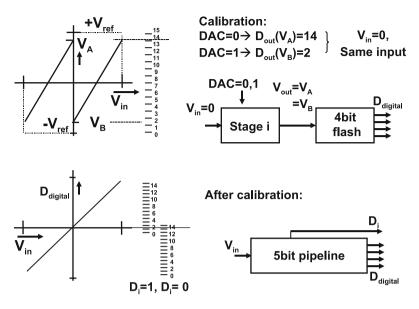

|   |      | 8.4.2    | Reduced Radix Converters with Digital Calibration     | 378 |

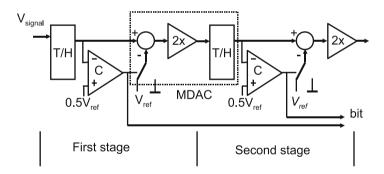

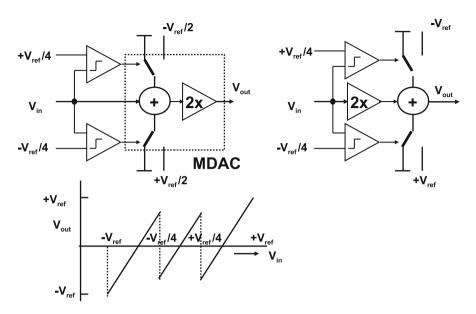

|   | 8.5  | 1.5 Bit  | Pipeline Analog-to-Digital Converter                  | 380 |

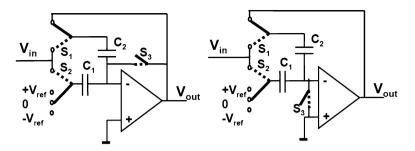

|   |      | 8.5.1    | Design of an MDAC Stage                               | 381 |

|   |      | 8.5.2    | Redundancy                                            | 384 |

|   |      | 8.5.3    | Pipeline Variants                                     | 385 |

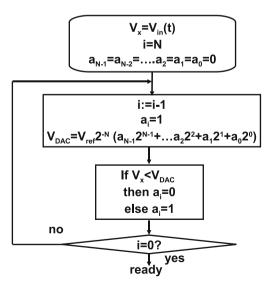

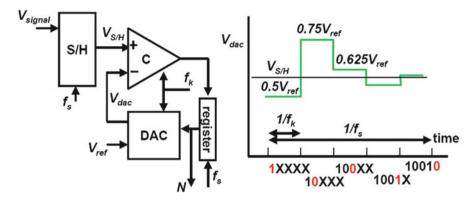

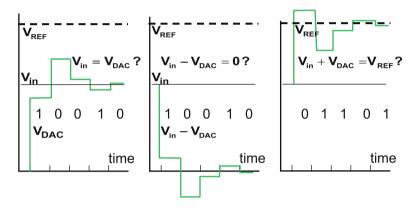

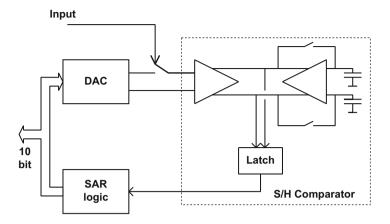

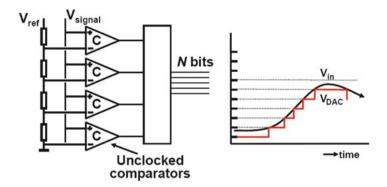

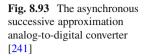

|   | 8.6  | Success  | sive Approximation Converters                         | 389 |

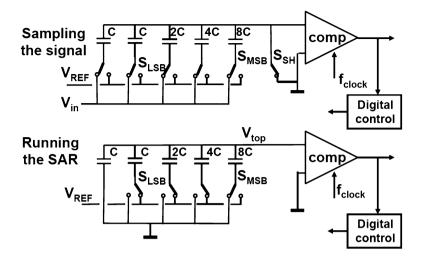

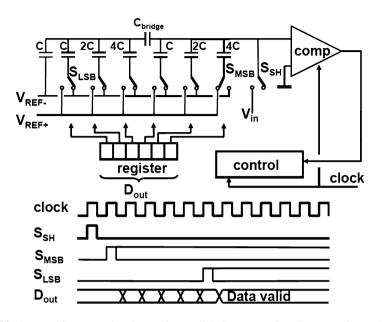

|   |      | 8.6.1    | Charge-Redistribution Conversion                      | 391 |

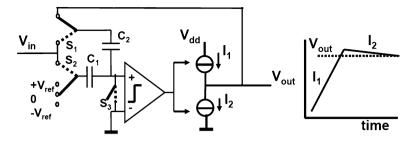

|   |      | 8.6.2    | Algorithmic Converters                                | 394 |

|   | 8.7  | Linear   | Approximation Converters                              | 398 |

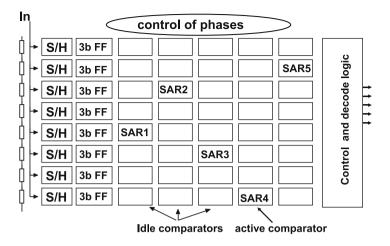

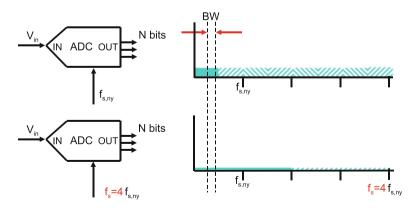

|   | 8.8  | Time-Iı  | nterleaving Time-Discrete Circuits                    | 400 |

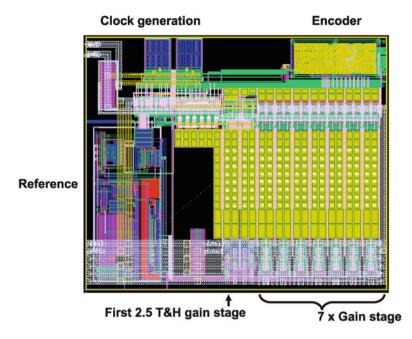

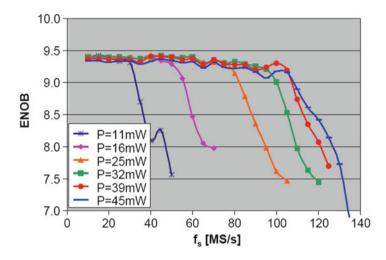

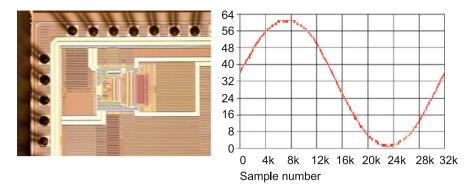

|   | 8.9  | Implem   | nentation Examples                                    | 404 |

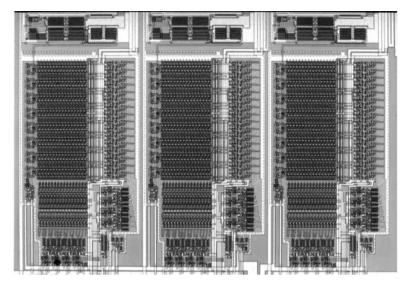

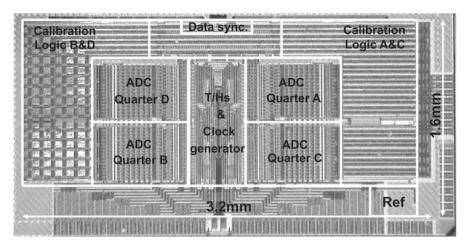

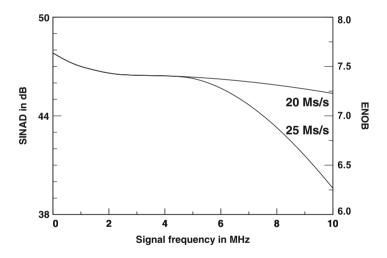

|   |      | 8.9.1    | Full-Flash Analog-to-Digital Converter                | 405 |

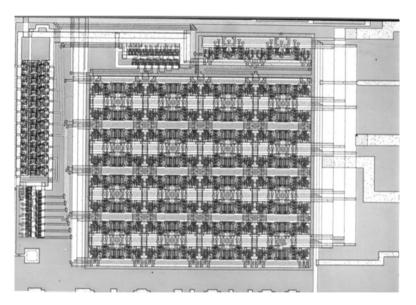

|   |      | 8.9.2    | Successive-Approximation Analog-to-Digital Converter. | 407 |

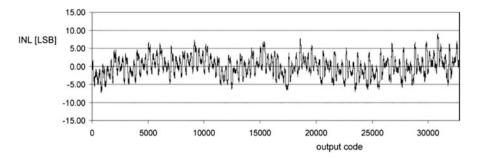

|   |      | 8.9.3    | Multistep Analog-to-Digital Converter                 | 407 |

|   |      | 8.9.4    | Comparison                                            | 409 |

|   | 8.10 | Other C  | Conversion Proposals                                  | 410 |

|   |      | 8.10.1   | Level-Crossing Analog-to-Digital Conversion           | 410 |

|   |      | 8.10.2   | Feedback Asynchronous Conversion                      | 411 |

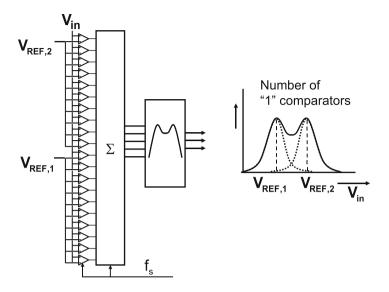

|    |       | 8.10.3   | Mismatch Dominated Conversion                       | 412 |

|----|-------|----------|-----------------------------------------------------|-----|

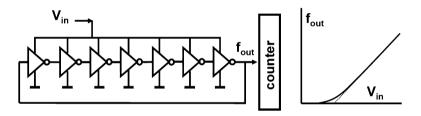

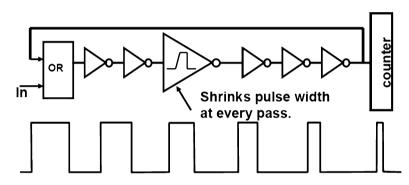

|    |       | 8.10.4   | Time-Related Conversion                             | 413 |

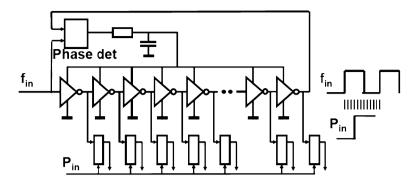

|    |       | 8.10.5   | Vernier/Nonius Principle                            | 415 |

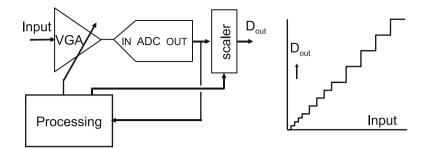

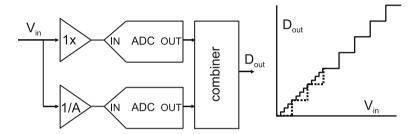

|    |       | 8.10.6   | Floating-Point Converter                            | 415 |

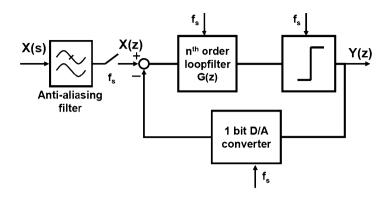

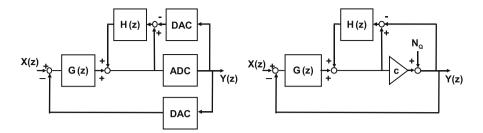

| 9  | Sigm  | a-Delta  | Modulation                                          | 419 |

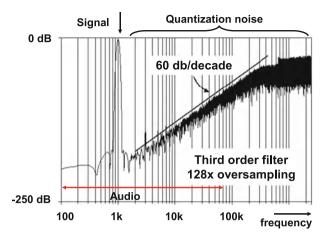

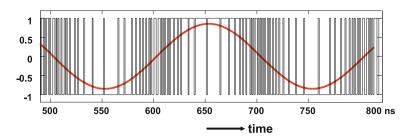

| -  | 9.1   |          | mpling                                              | 420 |

|    |       | 9.1.1    | Oversampling in Analog-to-Digital Conversion        | 420 |

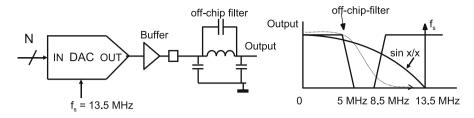

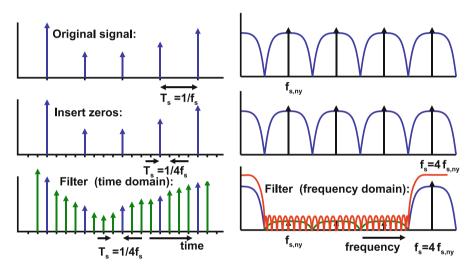

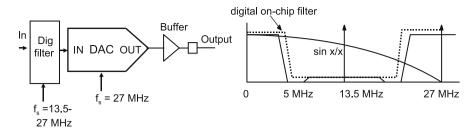

|    |       | 9.1.2    | Oversampling in Digital-to-Analog Conversion        | 421 |

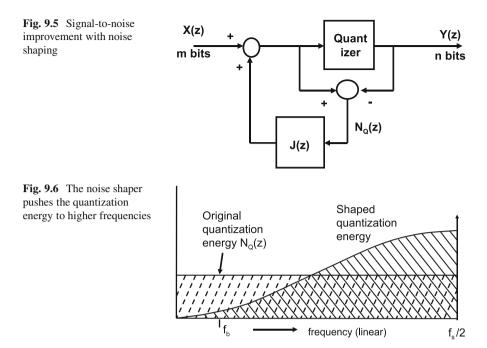

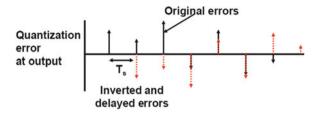

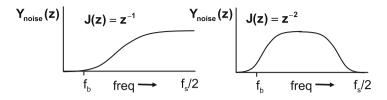

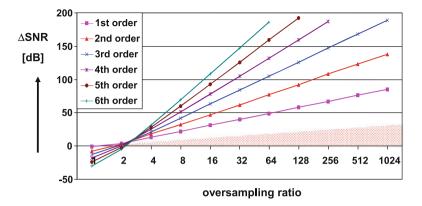

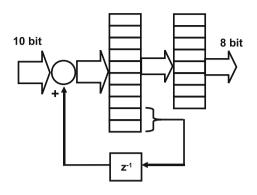

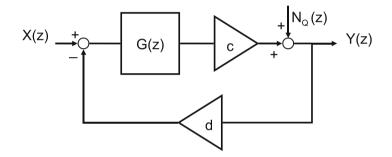

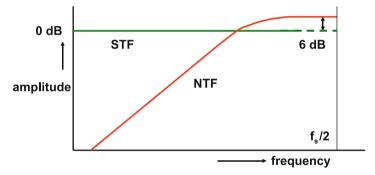

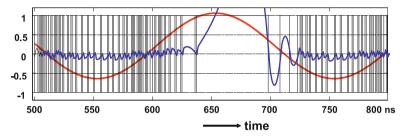

|    | 9.2   | Noise S  | Shaping                                             | 423 |

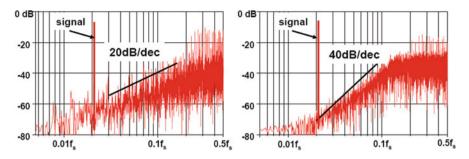

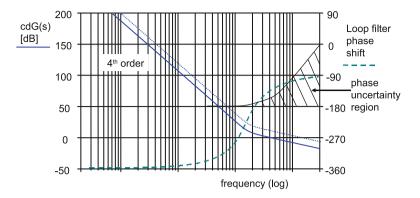

|    |       | 9.2.1    | Higher Order Noise Shaping                          | 426 |

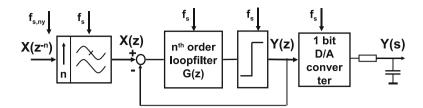

|    | 9.3   | Sigma-   | Delta Modulation                                    | 429 |

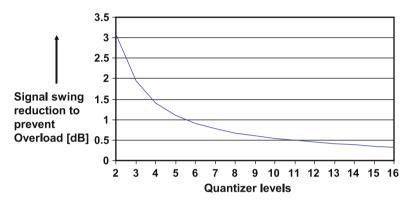

|    |       | 9.3.1    | Overload                                            | 432 |

|    |       | 9.3.2    | Sigma–Delta Digital-to-Analog Conversion            | 434 |

|    | 9.4   | Time-D   | Discrete Sigma–Delta Modulation                     | 435 |

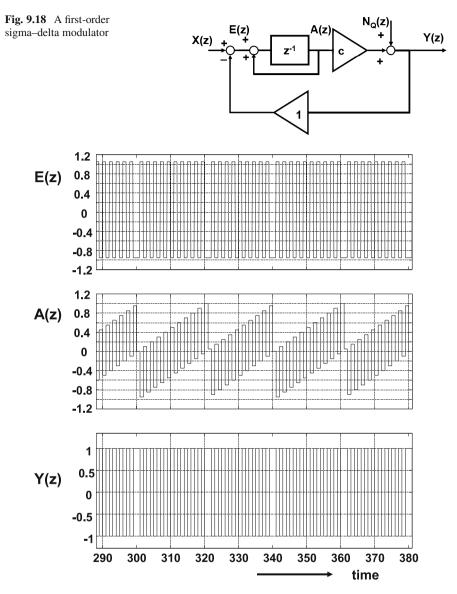

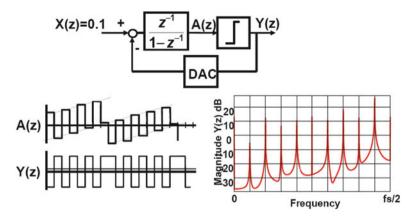

|    |       | 9.4.1    | First-Order Modulator                               | 435 |

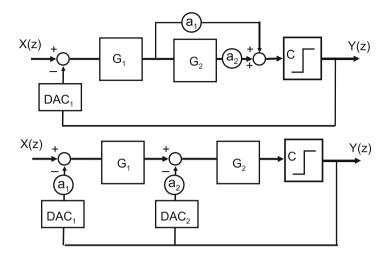

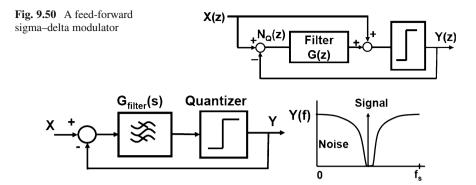

|    |       | 9.4.2    | Cascade of Integrators in FeedBack or Feed-Forward  | 437 |

|    |       | 9.4.3    | Second-Order Modulator                              | 439 |

|    |       | 9.4.4    | Circuit Design Considerations                       | 441 |

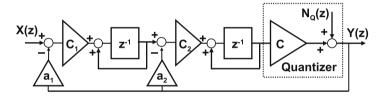

|    |       | 9.4.5    | Cascaded Sigma–Delta Modulator                      | 443 |

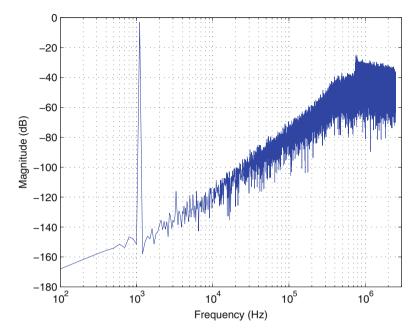

|    | 9.5   | Time-C   | Continuous Sigma–Delta Modulation                   | 445 |

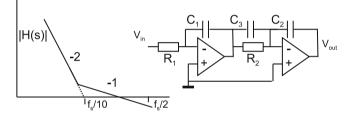

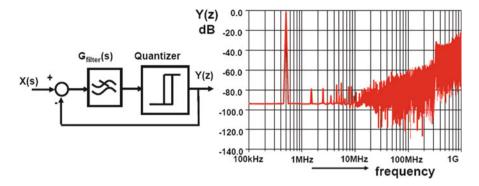

|    |       | 9.5.1    | First-Order Modulator                               | 445 |

|    |       | 9.5.2    | Higher-Order Sigma–Delta Converters                 | 449 |

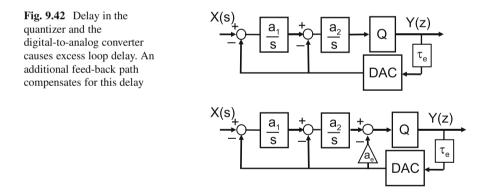

|    |       | 9.5.3    | Excess Loop Delay in Time-Continuous                |     |

|    |       |          | Sigma–Delta Conversion                              | 454 |

|    |       | 9.5.4    | Latency                                             | 455 |

|    | 9.6   |          | Discrete and Time-Continuous Sigma–Delta Conversion | 456 |

|    | 9.7   |          | it Sigma–Delta Conversion                           | 459 |

|    | 9.8   |          | Forms of Sigma–Delta Modulation                     | 462 |

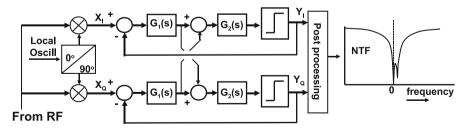

|    |       | 9.8.1    | Complex Sigma–Delta Modulation                      | 462 |

|    |       | 9.8.2    | Asynchronous Sigma–Delta Modulation                 | 463 |

|    |       | 9.8.3    | Input Feed-Forward Modulator                        | 463 |

|    |       | 9.8.4    | Band-Pass Sigma–Delta Converter                     | 464 |

|    |       | 9.8.5    | Sigma–Delta Loop with Noise Shaping                 | 465 |

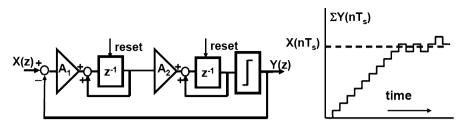

|    |       | 9.8.6    | Incremental Sigma–Delta Converter                   | 466 |

| 10 | Char  | acteriza | tion and Specification                              | 469 |

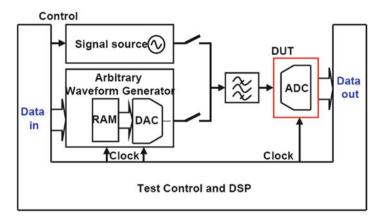

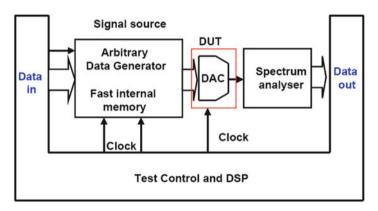

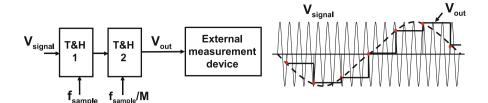

|    | 10.1  | Test Ha  | urdware                                             | 470 |

|    | 10.2  | Measur   | ement Methods                                       | 473 |

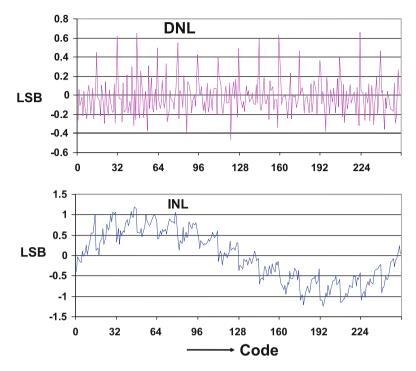

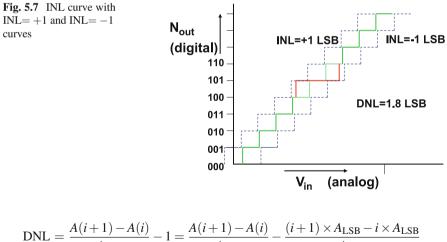

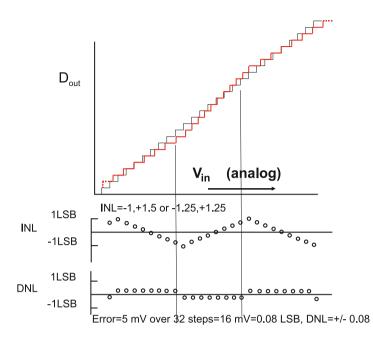

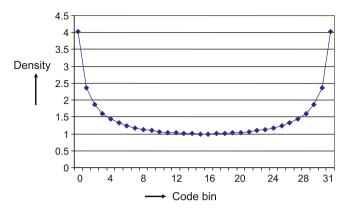

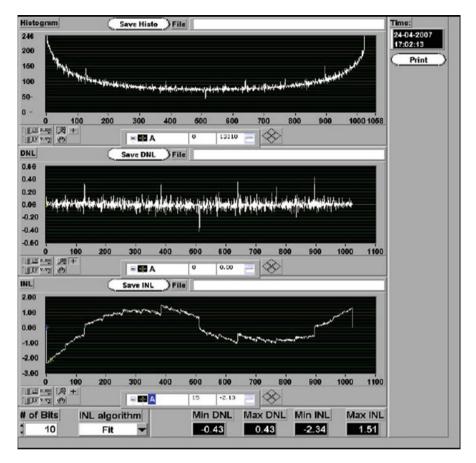

|    |       | 10.2.1   | INL and DNL                                         | 473 |

|    |       | 10.2.2   | Harmonic Behavior                                   | 476 |

|    | 10.3  | Self Te  | sting                                               | 479 |

| 11 | Techi | nology   |                                                     | 483 |

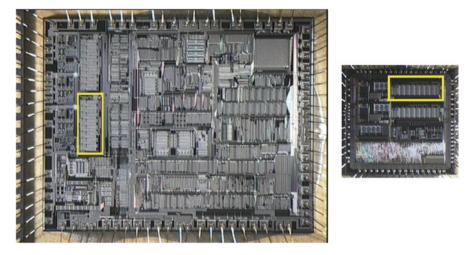

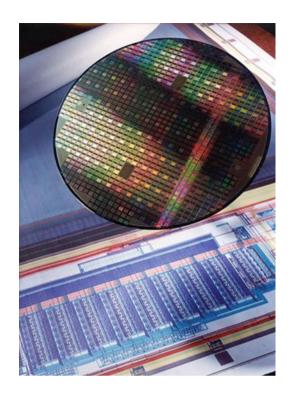

|    | 11.1  |          | logy Road Map                                       | 483 |

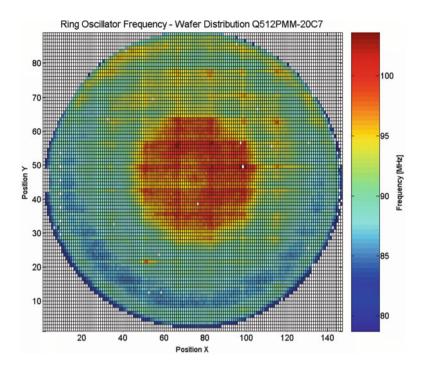

|    |       | 11.1.1   |                                                     | 484 |

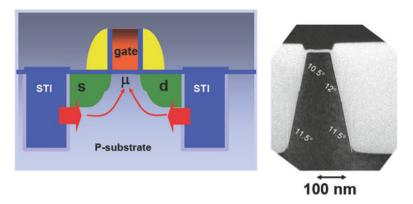

|     |           | 11.1.2   | Feature Size                                  | 486 |

|-----|-----------|----------|-----------------------------------------------|-----|

|     |           | 11.1.3   | Process Options                               | 487 |

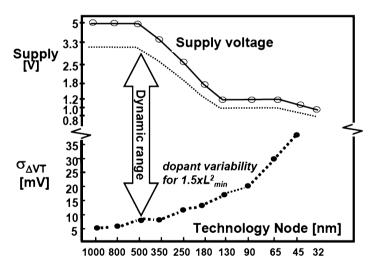

|     | 11.2      | Variabi  | lity: An Overview                             | 489 |

|     | 11.3      | Determ   | inistic Offsets                               | 491 |

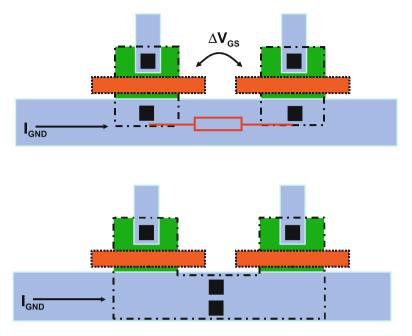

|     |           | 11.3.1   | Offset Caused by Electrical Differences       | 492 |

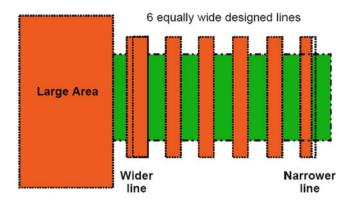

|     |           | 11.3.2   | Offset Caused by Lithography                  | 494 |

|     |           | 11.3.3   | Proximity Effects                             | 495 |

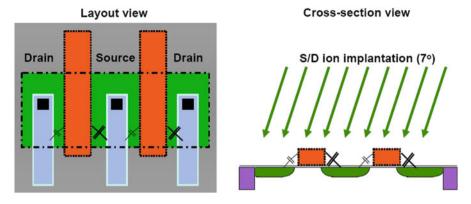

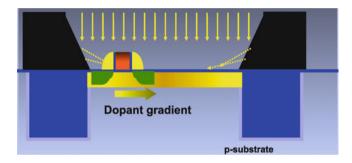

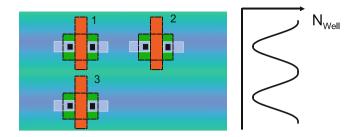

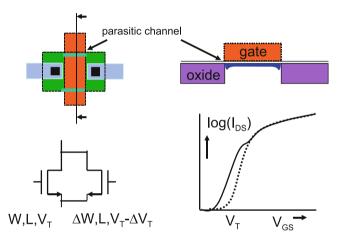

|     |           | 11.3.4   | Implantation-Related Effects                  | 496 |

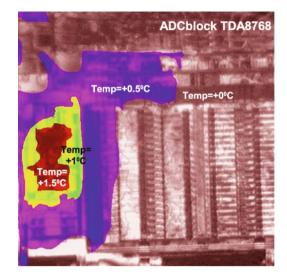

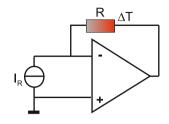

|     |           | 11.3.5   | Temperature Gradients                         | 499 |

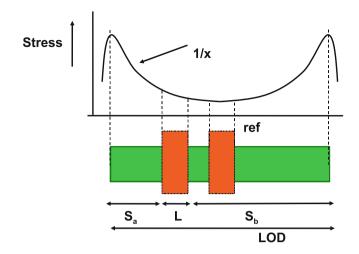

|     |           | 11.3.6   | Offset Caused by Stress                       | 500 |

|     |           | 11.3.7   | Offset Mitigation                             | 504 |

|     | 11.4      | Randor   | n Matching                                    | 507 |

|     |           | 11.4.1   | Random Fluctuations in Devices                | 507 |

|     |           | 11.4.2   | MOS Threshold Mismatch                        | 510 |

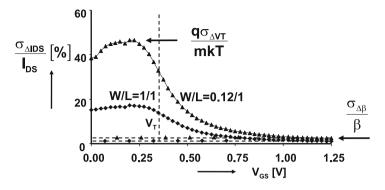

|     |           | 11.4.3   | Current Mismatch in Strong and Weak Inversion | 513 |

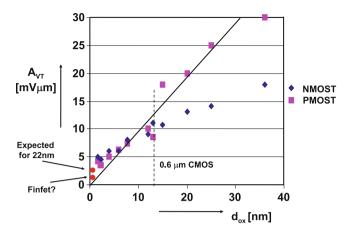

|     |           | 11.4.4   | Mismatch for Various Processes                | 515 |

|     |           | 11.4.5   | Application to Other Components               | 519 |

|     |           | 11.4.6   | Modeling Remarks                              | 520 |

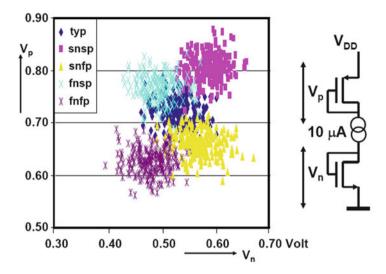

|     | 11.5      | Conseq   | uences for Design                             | 521 |

|     |           | 11.5.1   | Analog Design                                 | 521 |

|     |           | 11.5.2   | Digital Design                                | 522 |

|     |           | 11.5.3   | Drift                                         | 524 |

|     |           | 11.5.4   | Limits of Power and Accuracy                  | 525 |

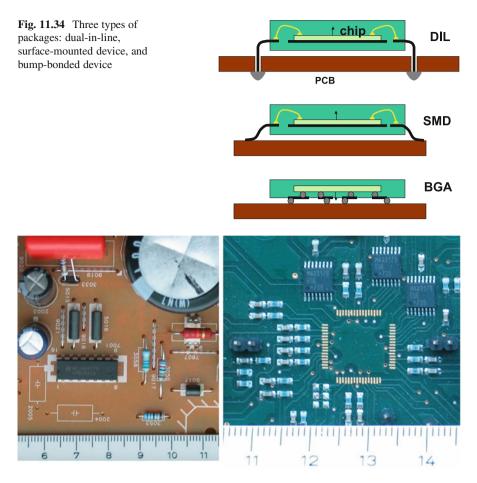

|     | 11.6      | Packag   | ing                                           | 526 |

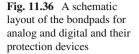

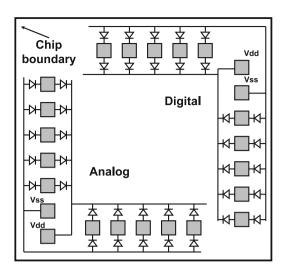

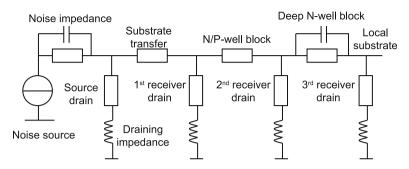

|     | 11.7      | Substra  | te Noise                                      | 530 |

| 12  | Syste     | m Asneo  | ets of Conversion                             | 537 |

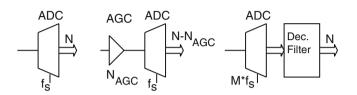

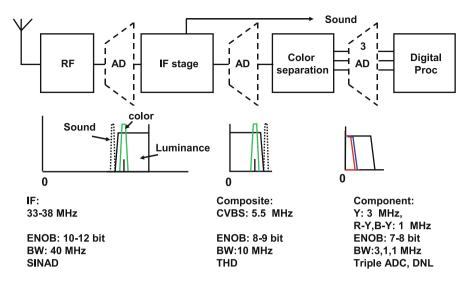

|     | 12.1      |          | Aspects                                       | 539 |

|     |           | 12.1.1   | Specification of Functionality                | 541 |

|     |           | 12.1.2   | Signal Processing Strategy                    | 542 |

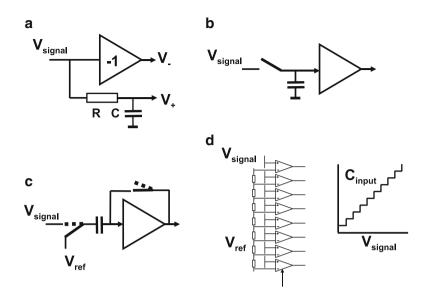

|     |           | 12.1.3   | Input Circuits                                | 544 |

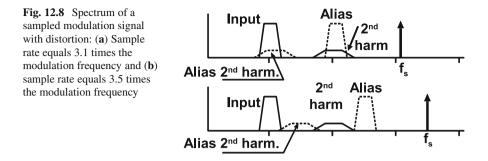

|     |           | 12.1.4   | Conversion of Modulated Signals               |     |

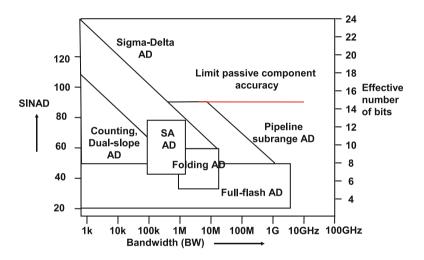

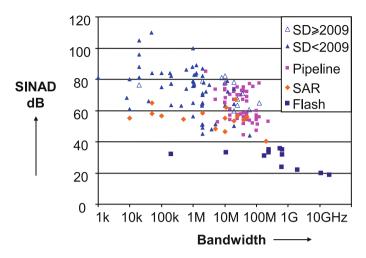

|     | 12.2      |          | ring Converters                               |     |

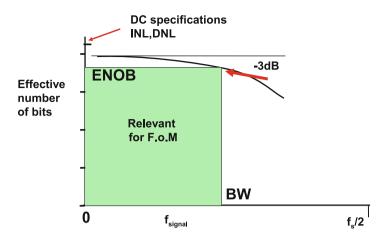

|     | 12.3      |          | of Conversion                                 |     |

|     |           |          |                                               |     |

| Dof | oronoo    | <b>a</b> |                                               | 557 |

| Rel | erence    | 5        |                                               | 557 |

| Abo | out the   | Author   |                                               | 573 |

|     | , at the  | - suchor |                                               | 515 |

| Ind | <b>ex</b> |          |                                               | 575 |

|     |           |          |                                               |     |

## List of Symbols

| Symbol       | Description                                          | Unit symbol             |

|--------------|------------------------------------------------------|-------------------------|

| A            | Area                                                 | cm <sup>2</sup>         |

| С            | Capacitance                                          | F                       |

| $C_{\rm ox}$ | Oxide capacitance                                    | F/cm <sup>2</sup>       |

| $D_n$        | Diffusion coefficient of electrons                   | cm <sup>2</sup> /sec    |

| $d_{\rm ox}$ | Oxide thickness                                      | $cm = 10^8 \text{\AA}$  |

| Ε            | Electric field                                       | V/cm                    |

| $E_{Fn}$     | Fermi energy level of electrons                      | eV                      |

| $E_{Fp}$     | Fermi energy level of holes                          | eV                      |

| $E_G$        | Band gap energy                                      | 1.205 eV                |

| $E_i$        | Energy level of an intrinsic semiconductor           | eV                      |

| f            | Frequency                                            | Hz                      |

| $f_c$        | Clock frequency                                      | Hz                      |

| $f_i$        | Frequency of input signal                            | Hz                      |

| $f_s$        | Sample rate                                          | Hz                      |

| H            | Transfer function                                    | 1                       |

| Ι            | Large-signal or DC current                           | А                       |

| i            | Small signal current                                 | А                       |

| J            | Current density                                      | A/cm <sup>2</sup>       |

| $J_n$        | Electron current density                             | A/cm <sup>2</sup>       |

| $J_p$        | Hole current density                                 | A/cm <sup>2</sup>       |

| Κ            | Substrate voltage influence on the threshold voltage | $\sqrt{\mathrm{V}}$     |

| k            | Boltzmann's constant                                 | $1.38	imes10^{-23}$ J/K |

| L            | Length of transistor gate                            | cm/µm                   |

| $L_w$        | Inductance of a wire                                 | Н                       |

| М            | Multiplex factor                                     | 1                       |

| Ν            | Resolution                                           | 1                       |

| $N_a$        | Substrate doping concentration                       | $\mathrm{cm}^{-3}$      |

| п            | Volume density of electrons                          | $\mathrm{cm}^{-3}$      |

| $n_i$                                              | Intrinsic charge volume density (300 K)                     | $1.4 \times 10^{10} \text{ cm}^{-3}$      |

|----------------------------------------------------|-------------------------------------------------------------|-------------------------------------------|

| р                                                  | Volume density of holes                                     | $cm^{-3}$                                 |

| $p_{p0}$                                           | Volume density of holes in a <i>p</i> -substrate in equili  | brium cm <sup>-3</sup>                    |

| R                                                  | Resistance                                                  | Ω                                         |

| Q                                                  | Charge                                                      | С                                         |

| q                                                  | Electron charge                                             | $1.6\times10^{-19}C$                      |

| Т                                                  | Time period                                                 | S                                         |

| Т                                                  | Absolute temperature                                        | K                                         |

| $T_0$                                              | Reference temperature                                       | K                                         |

| $T_s$                                              | Sample period                                               | S                                         |

| t                                                  | Time as a running variable                                  | S                                         |

| V                                                  | Bias or DC potential                                        | V                                         |

| ν                                                  | Small signal voltage                                        | V                                         |

| $V_{\rm DD}$                                       | Positive power supply                                       | V                                         |

| $V_{\rm DS}$                                       | Drain potential with respect to the source potentia         | al V                                      |

| $V_{\rm FB}$                                       | Flat-band voltage                                           | V                                         |

| $V_G$                                              | Gate potential with respect to ground                       | V                                         |

| $V_{\rm GS}$                                       | Gate potential with respect to the source potential         | l V                                       |

| $V_{\mathrm{T}}$                                   | MOS transistor threshold voltage                            | V                                         |

| W                                                  | Width of transistor channel                                 | cm/µm                                     |

| X, Y                                               | General input and output variable                           | . 1                                       |

| x, y, z                                            | Dimension variables                                         | cm/µm                                     |

| Ζ                                                  | Complex impedance                                           | Ω                                         |

| β                                                  | Current gain factor of MOS transistor: $W\beta_{\Box}/L$    | $A/V^2$                                   |

| $\beta_{\Box}$                                     | Current gain factor of a square MOS transistor $p_{\Box}/E$ | $A/V^2$                                   |

| $\Delta P$                                         | Difference between two parameters $P_1 - P_2$               | 2 <b>U</b> V                              |

| ε                                                  | Permittivity in vacuum                                      | $8.854 	imes 10^{-14}$ F/cm               |

| $\varepsilon$<br>$\varepsilon_{\rm ox}\varepsilon$ | Permittivity in silicon dioxide                             | $3.45 \times 10^{-13}$ F/cm               |

| $\mathcal{E}_{0X}\mathcal{E}$                      | Permittivity in silicon                                     | $10.5 \times 10^{-13}$ F/cm               |

| $\phi_F$                                           | Potential difference between intrinsic                      | V                                         |

| $\Psi r$                                           | and hole Fermi level                                        | ,                                         |

| $\mu_0$                                            | Magnetic permeability in vacuum $4\pi$                      | $\times 10^{-7}$ H/m or N/A <sup>-2</sup> |

| $\mu_n, \mu_p$                                     | Mobility of electrons and holes                             | cm <sup>2</sup> /Vs                       |

| π                                                  | Angular constant                                            | 3.14159                                   |

| Ψ                                                  | Electrostatic potential                                     | V                                         |

| $\psi_B$                                           | Electrostatic potential at which strong inversion s         | tarts V                                   |

| $\dot{\psi}_s$                                     | Electrostatic potential at the interface                    | V                                         |

| $\sigma_{\!\Delta P}$                              | Standard deviation of $\Delta P$                            |                                           |

| $\sigma_n$                                         | Electron capture cross-section                              | $5 	imes 10^{-15} \mathrm{~cm}^2$         |

| τ                                                  | Time-constant                                               | S                                         |

| $\omega = 2\pi f$                                  | Angular or radian frequency                                 | rad/s                                     |

|                                                    |                                                             |                                           |

## **Reference Tables and Figures**

| Table 1.1   | Key functions in analog-to-digital conversion                    | 3   |

|-------------|------------------------------------------------------------------|-----|

| Table 2.1   | Multiplier abbreviations                                         | 6   |

| Table 2.2   | Elementary algebraic functions                                   | 6   |

| Table 2.6   | Standard manipulations for derivatives of functions              | 8   |

| Table 2.8   | Taylor series expansions                                         | 9   |

| Table 2.5   | Goniometric relations                                            | 7   |

| Table 2.10  | Laplace transforms                                               | 19  |

| Table 2.9   | Fourier series expansions                                        | 12  |

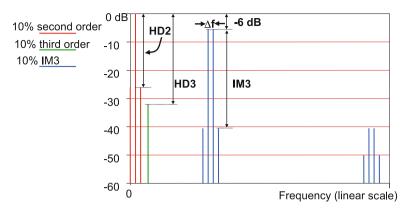

| Figure 2.5  | Distortion relations: HD2, HD3 and IM3                           | 18  |

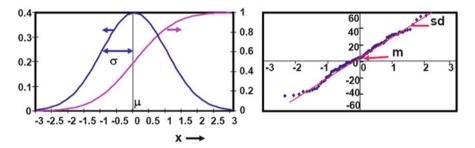

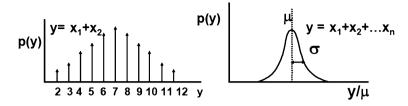

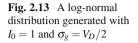

| Table 2.11  | Probability of Gauss distribution                                | 25  |

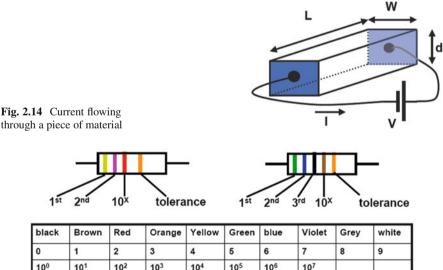

| Figure 2.15 | Color coding for discrete resistors                              | 31  |

| Table 2.12  | Resistivity of (semi-)conductors                                 | 32  |

| Table 2.15  | Electrostatic properties of semiconductors                       | 58  |

| Figure 2.27 | Resistivity of doped silicon                                     | 58  |

| Table 2.16  | Resistors in 0.18 µm to 65 nm CMOS                               | 59  |

| Table 2.18  | Diffusion capacitances in $0.25\mu m$ and $65nm$ CMOS            | 70  |

| Table 2.19  | Passive capacitances for 0.18 µm to 90 nm CMOS                   | 72  |

| Table 2.17  | Data for vertical pnp transistors                                | 66  |

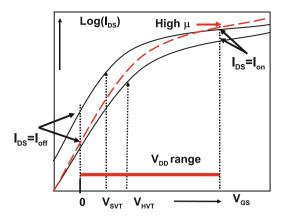

| Figure 2.44 | Current factor for various MOS processes                         | 78  |

| Table 2.20  | Transistor parameters from $0.8\mu m$ to $28nm$ CMOS             | 79  |

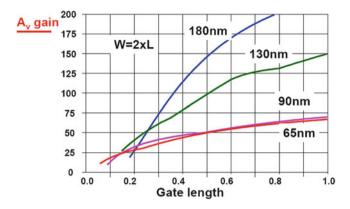

| Figure 2.48 | The voltage gain of a transistor versus gate length and process  | 84  |

| Table 2.24  | Low-pass filter functions                                        | 109 |

| Figure 2.73 | Amplifier classes: A, B, AB, C, D, E                             | 120 |

| Figure 3.9  | Suppression of alias filters                                     | 176 |

| Figure 3.13 | The signal-to-noise ration as a function of jitter and bandwidth | 181 |

| Figure 3.10 | kT/C noise                                                       | 176 |

|             |                                                                  |     |

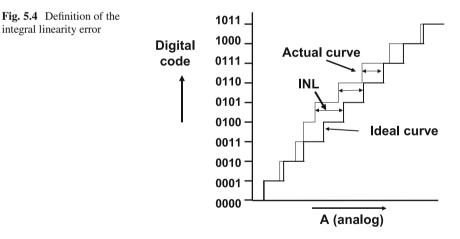

| Figure 5.4    | Definition of integral non-linearity                                  |     |

|---------------|-----------------------------------------------------------------------|-----|

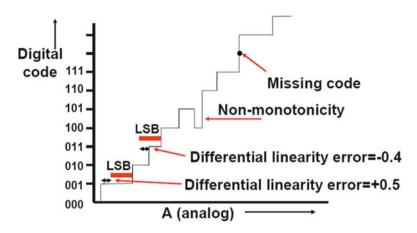

| Figure 5.5    | Definition of differential non-linearity                              | 232 |

| Table 5.1     | Thermal noise and quantization error properties                       | 238 |

| Equation 5.13 | Ratio between signal and quantization power                           | 239 |

| Table 7.1     | Digital representations                                               | 268 |

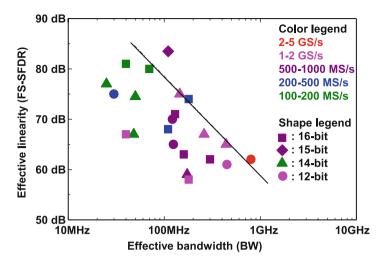

| Figure 7.21   | SFDR versus bandwidth for current-steering DACs.                      | 289 |

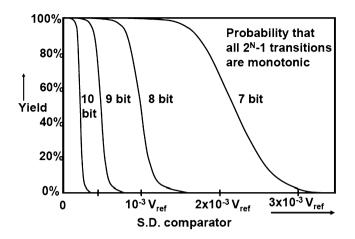

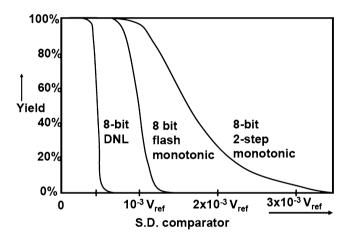

| Figure 8.27   | Yield on monotonicity versus comparator random offset                 | 352 |

| Table 8.1     | Mismatch in full-flash conversion                                     | 354 |

| Figure 9.9    | Signal-to-noise gain in noise-shapers and sigma-delta                 | 428 |

| Table 10.1    | Characterization parameters for analog-to-digital conversion          | 470 |

| Table 11.1    | Excerpt from the ITRS 2011                                            | 485 |

| Table 11.3    | Classification of variance                                            | 489 |

| Table 11.7    | Guidelines for low-offset layout                                      | 505 |

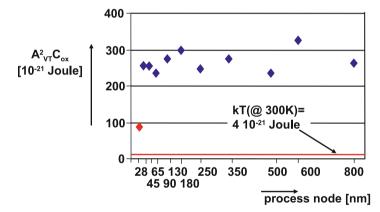

| Figure 11.27  | Mismatch factor $A_{V_{T}}$ versus oxide thickness/process generation | 516 |

| Table 11.9    | Matching coefficients of various devices                              | 519 |

| Table 11.11   | Package names                                                         | 528 |

| Table 12.2    | Analog-to-digital system requirements                                 | 541 |

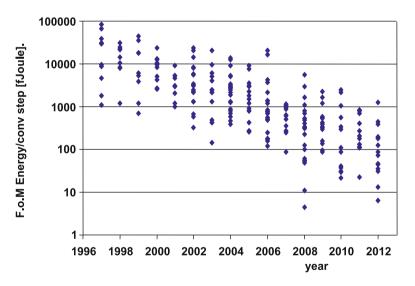

| Table 12.5    | Power efficiency of ISSCC published converters                        | 552 |

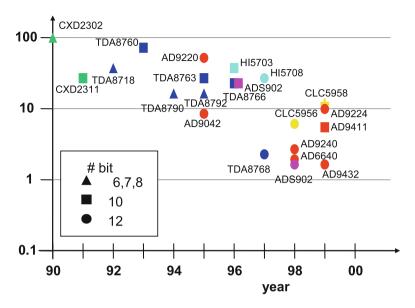

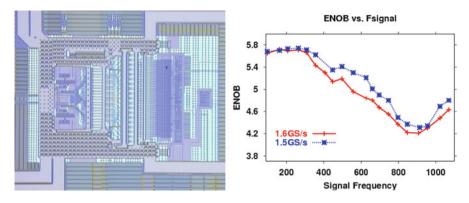

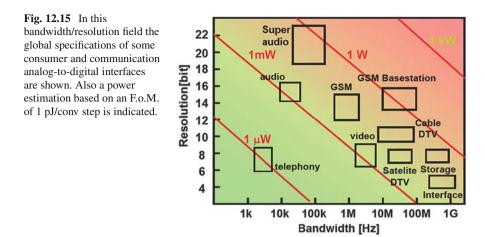

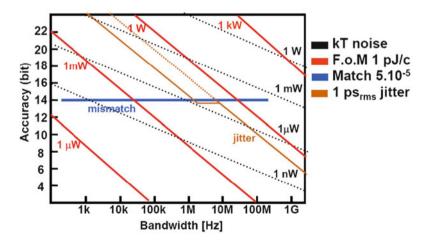

| Figure 12.12  | Figure of merit of analog-to-digital converters                       | 551 |

| Figure 12.16  | Limits for analog-to-digital conversion                               | 554 |

### Chapter 1 Introduction

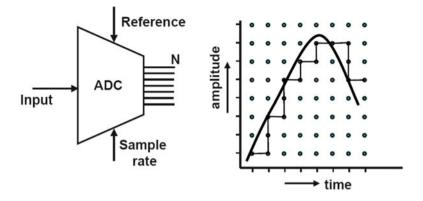

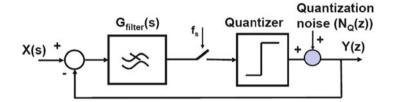

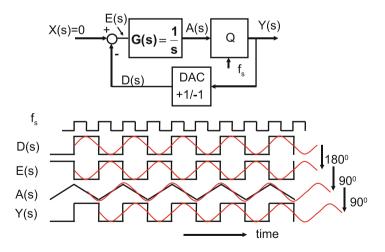

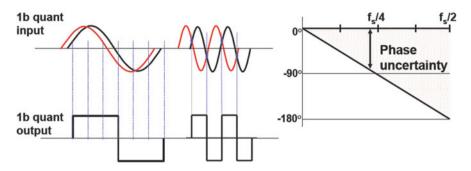

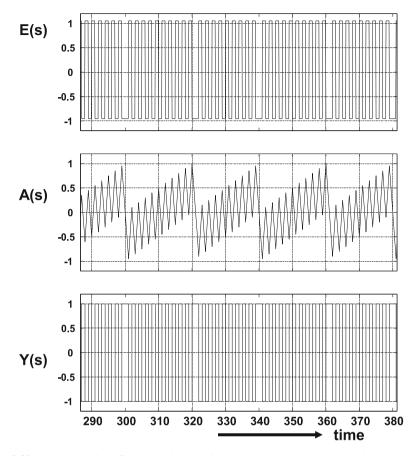

**Abstract** An analog-to-digital converter is an essential building block in modern signal processing. Both the analog-to-digital conversion as well as the digital-to-analog conversion are key functions for optimally exploiting the capabilities of the digital signal processing core. Three basic processes are distinguished in analog-to-digital conversion: the transition between the time-continuous domain and time-discrete domain, the quantization of the signal amplitude, and the relation between physical quantities and numerical quantities.

Analog-to-digital conversion is everywhere around us. In all forms of electronic equipment the analog-to-digital converter links our physical world to digital computing machines. This development has enabled all the marvelous functionality that has been introduced over the last 30 years, from mobile phone to internet from medical imaging machines to handheld television.

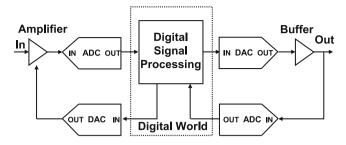

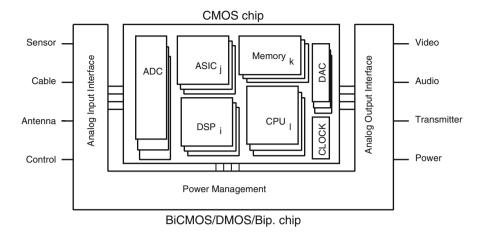

Pure analog electronics circuits can do a lot of signal processing in a cheap and well-established way. Many signal processing functions are so simple that analog processing serves the needs (audio amplification, filtering, radio). In more complex situations, analog processing however lacks required functionality. There digital signal processing offers crucial extensions of analog functionality. The most important advantages of digital processing over analog processing are a perfect storage of digitized signals, unlimited signal-to-noise ratio, the option to carry out complex calculations, and the possibility to adapt the algorithm of the calculation to changing circumstances. If an application wants to use these advantages, analog signals have to be converted with high quality into a digital format in an early stage of the processing chain. And at the end of the digital processing the conversion has to be carried out in the reverse direction. The digital-to-analog translates the outcome of the signal processing into signals that can be rendered as a picture or sound. This makes analog-to-digital conversion a crucial element in the chain between our world of physical quantities and the rapidly increasing power of digital signal processing. Figure 1.1 shows the analog-to-digital converter (abbreviated A/D

Fig. 1.1 The analog-to-digital and digital-to-analog converters are the ears and eyes of a digital system

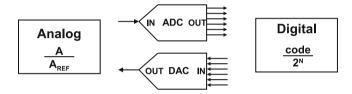

Fig. 1.2 In analog-to-digital conversion a connection is made between the analog world of physical quantities and the digital world of numbers and bits

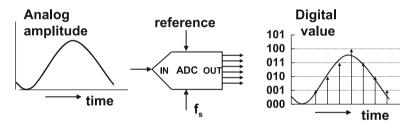

Fig. 1.3 Functions of the analog-to-digital converter: sampling, quantizing, and linking to a reference

converter or ADC) as the crucial element in a system with combined analog and digital functionality.

The analog-to-digital converters and digital-to-analog converters discussed in this book convert high-resolution and high-speed signals to and from the digital domain. The basics of the conversion process is shown in Fig. 1.2. In the analog domain a ratio exists between the actual signal and a reference quantity. This ratio is reflected in the digital domain, where the digital code is a fraction of the available word width. The analog-to-digital converter tries to find an optimum match between these ratios at any moment in time. However, an essential rounding error must be accepted. Signals in the digital domain differ from analog signals, which exist in the physical world, because digital signal are sampled and quantized, Fig. 1.3. Sampled signals only have meaning at their sample moments as given by the sample frequency. Moreover digital signals are arithmetic quantities, which are

| Table 1.1         Key functions           in analog-to-digital         Image: Comparison of the second | Analog-to-digital                                                                    | Digital-to-analog                                                                  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|

| conversion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Time discretization<br>Amplitude discretization<br>Reference to<br>a conversion unit | Holding the signal<br>Amplitude restoration<br>Reference from<br>a conversion unit |

only meaningful in the physical world while there is somewhere an assignment that relates the digital number range to a physical reference value. These three main functions characterize the analog-to-digital converter see Table 1.1. These functions will be visible in each stage of the discussion of analog-to-digital conversion and are reflected in the setup of this book.

### 1.1 About This Book

An analog-to-digital converter and a digital-to-analog converter are electronics circuits that are designed and fabricated in silicon IC technology. The main focus in this book is on CMOS realizations.

Chapter 2 summarizes the main physics and mathematics for understanding the operation of analog-to-digital converters. This chapter is meant to refresh existing knowledge.

In Chaps. 3–6 the three basic functions for conversion are analyzed. Chapter 3 describes the sampling process and gives guidelines for the different choices around sampling in analog-to-digital conversion design. The design challenges around the sampling process are discussed in the design of sample-and-hold circuits in Chap. 4. Both sampling and quantization are nonlinear operations, resulting in undesired behavior. The combination of sampling and quantization results in a fundamental error: the quantization error. The attainable performance of every analog-to-digital conversion is fundamentally limited by this error as is described in Chap. 5. Chapter 6 deals with the generation and handling of reference voltages.

The main task of a designer is to construct circuits. Chapter 7 describes the basics of digital-to-analog converter circuit design and some implementations of digital-to-analog converters. The design of analog-to-digital converters is elaborated in Chap. 8. Oversampling and sigma delta conversion are a special class of conversion techniques and are discussed in Chap. 9.

The measurement methods for analog-to-digital converters and specification points are the subject of Chap. 10. Chapter 11 deals with some of the boundary conditions in conversion due to technological and physical limitations. Finally Chap. 12 deals with system aspects of the application of analog-to-digital conversion like sample frequency choices and the various forms of input handling. This section also introduces figure-of-merits for conversion and compares the various implementation forms. In this way an optimal converter for a given system situation can be chosen. Several books have been published in the field of analog-to-digital conversion. One of the first books was published by Seitzer [1] in 1983 describing the basic principles. Van der Plassche [2] in 1994 and 2003 and Razavi [3] in 1994 discuss extensively bipolar and CMOS realizations. Jespers [4] and Maloberti [5] address the theme on a graduate level. These textbooks review the essential aspects and focus on general principles, circuit realizations, and their merits.

### Chapter 2 Components and Definitions

**Abstract** Mathematics and physics form the basis for electronic design and also for analog-to-digital conversion. This chapter reviews the necessary mathematics and physics. In the mathematics section, the essential transformations of signals, decomposition in harmonic components, and statistical methods are summarized. Some examples are given that are applicable to problems in the following chapters.

The physics sections deal with the behavior of elementary components: resistors, capacitors, and inductors. These components are reviewed with application in integrated circuits in mind. Also the active elements, bipolar and MOS devices, are described and the main model features highlighted. Small-signal and large-signal behavior and stability are discussed. The statistical behavior of large numbers of these devices is reviewed. This chapter concludes with a number of basic circuits, from the differential pair to an oscillator.

An electronic engineer combines in his/her work elements of mathematics, physics, network theory, and other scientific disciplines. The creative combination of the elements allows the engineer to bridge fundamental theoretical insights with practical realizations. Often these theoretical disciplines are phrased in mathematical descriptions. Therefore it is relevant to start this book with a summary of these disciplines.

### 2.1 Mathematical Tools

Events and processes in semiconductor devices span a large range of numbers. Abbreviations for these numbers are shown in Table 2.1. The words "billion" and "trillion" must be avoided as they refer to different quantities in Europe and the USA.<sup>1</sup>

<sup>&</sup>lt;sup>1</sup>This confusion is related to the use of the "long-scale" numbering system in continental Europe and the "short-scale" numbering system in the USA and the UK.

| Name   | Abbreviation | Multiplier        |

|--------|--------------|-------------------|

| Googol |              | 10 <sup>100</sup> |

| Exa    | Е            | $10^{18}$         |

| Peta   | Р            | $10^{15}$         |

| Tera   | Т            | $10^{12}$         |

| Giga   | G            | 109               |

| Mega   | Μ            | $10^{6}$          |

| kilo   | k            | $10^{3}$          |

| hecto  | h            | $10^{2}$          |

| deca   | da           | 10                |

| unity  |              | 1                 |

| deci   | d            | $10^{-1}$         |

| centi  | с            | $10^{-2}$         |

| milli  | m            | $10^{-3}$         |

| micro  | μ            | $10^{-6}$         |

| nano   | n            | $10^{-9}$         |

| pico   | р            | $10^{-12}$        |

| femto  | f            | $10^{-15}$        |

| atto   | а            | 10 <sup>-18</sup> |

**Table 2.1**Multiplierabbreviations

Table 2.2

Elementary algebraic functions [6–8]

| $n! = 1 \times 2 \times 3 \cdots \times n$                                 | 0! = 1,  1! = 1                                    |

|----------------------------------------------------------------------------|----------------------------------------------------|

| $\binom{n}{m} = \frac{n!}{m!(n-m)!}$                                       | $\binom{n}{n} = \binom{n}{0} = 1$                  |

| $(a+b)^n = a^n + {n \choose 1} a^{n-1}b + {n \choose 2} a^{n-2}b^2 \dots$  | $(a+b)^2 = a^2 + 2ab + b^2$                        |

| $+\binom{n}{n-1}ab^{n-1}+b^n$                                              | $(a+b)^3 = a^3 + 3a^2b + 3ab^2 + b^3$              |

| $a^{n} - b^{n} = (a - b)(a^{n-1} + a^{n-2}b + \dots + ab^{n-2} + b^{n-1})$ | $a^2 - b^2 = (a - b)(a + b)$                       |

| $ax^{2} + bx + c = 0,  x_{1,2} = \frac{-b \pm \sqrt{b^{2} - 4ac}}{2a}$     |                                                    |

| $\sum_{i=0}^{n} i = \frac{n(n+1)}{2}$                                      |                                                    |

| $\sum_{i=0}^{n} r^{i} = \frac{1 - r^{n+1}}{1 - r}$                         | $\sum_{i=0}^{\infty} r^i = \frac{1}{1-r}   r  < 1$ |

| $a^b = e^{b \ln a}$                                                        | $a^0 = e^0 = 1$ $e = 2.71828$                      |

| $\ln(b) = \ln(a) \times^a \log(b)$                                         | $\ln(10) = 2.303,  {}^{10}\log(10^n) = n$          |

|                                                                            | $^{10}\log(2) = 0.301,  ^{10}\log(3) = 0.477$      |

Mathematical expressions are built from functions of variables: y = f(x). Table 2.2 lists some elementary mathematical functions and equations. Extensive lists of mathematical functions for engineers are found in [6–8]. When calculations in two or three dimensions are too complicated, it can help to map the problem on a circle or a sphere. Especially time-repetitive signals and electromagnetic field calculations use cyclic and spherical functions to simplify the analysis. Table 2.3

| Table 2.3       Circle and sphere         functions [6-8] | Perimeter of a circle<br>Area of a circle<br>Surface of a sphere<br>Volume of a sphere | $\frac{2\pi r}{\pi r^2}$ $\frac{4\pi r^2}{4\pi r^3}$ |

|-----------------------------------------------------------|----------------------------------------------------------------------------------------|------------------------------------------------------|

|                                                           | volume of a sphere                                                                     | $\frac{\overline{3}^{n}}{3}$                         |

| Table 2.4         Complex notation [6–8]                            |                                                                                                              |

|---------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|

| $j^2 = -1$                                                          | $ a+jb ^2 = a^2 + b^2$                                                                                       |

| z = a + jb                                                          | Conjugate(z): $z^* = a - jb$                                                                                 |

| Real part $(z) = \operatorname{Re}(z) = \operatorname{Re}(z^*) = a$ | Imaginary $part(z) = Im(z) = -Im(z^*) = b$ ,                                                                 |

| $ z ^2 = z \times z^* = a^2 + b^2$                                  | Phase(z) = arg(z) = arctan $\left(\frac{\text{Im}(z)}{\text{Re}(z)}\right)$                                  |

| $e^{\pm j\alpha} = \cos(\alpha) \pm j\sin(\alpha)$                  | $\sin(\alpha) = \frac{e^{j\alpha} - e^{-j\alpha}}{2j},  \cos(\alpha) = \frac{e^{j\alpha} + e^{-j\alpha}}{2}$ |

| Table 2.5         Goniometrical relations used in this book                |                                                                                        |  |

|----------------------------------------------------------------------------|----------------------------------------------------------------------------------------|--|

| $\sin(-\alpha) = -\sin(\alpha)$                                            | $\cos(-\alpha) = \cos(\alpha)$                                                         |  |

| $\sin(\alpha) = \cos\left(\frac{\pi}{2} - \alpha\right)$                   | $\cos(\alpha) = \sin\left(\frac{\pi}{2} - \alpha\right)$                               |  |

|                                                                            | $\sin\left(\frac{\pi}{4}\right) = \cos\left(\frac{\pi}{4}\right) = \frac{1}{\sqrt{2}}$ |  |

| $\tan(\alpha) = \frac{\sin(\alpha)}{\cos(\alpha)} = a$                     | $\arctan(a) = \alpha$                                                                  |  |

| $\sin^2(\alpha) + \cos^2(\alpha) = 1$                                      |                                                                                        |  |

| $\sin(2\alpha) = 2\sin(\alpha)\cos(\alpha)$                                | $\cos(2\alpha) = \cos^2(\alpha) - \sin^2(\alpha) = 2\cos^2(\alpha) - 1$                |  |

| $\sin(3\alpha) = -4\sin^3(\alpha) + 3\sin(\alpha)$                         | $\cos(3\alpha) = 4\cos^3(\alpha) - 3\cos(\alpha)$                                      |  |

| $\sin(\alpha + \beta) = \sin(\alpha)\cos(\beta) + \cos(\alpha)\sin(\beta)$ | $\cos(\alpha + \beta) = \cos(\alpha)\cos(\beta) - \sin(\alpha)\sin(\beta)$             |  |

| $\sin(\alpha - \beta) = \sin(\alpha)\cos(\beta) - \cos(\alpha)\sin(\beta)$ | $\cos(\alpha - \beta) = \cos(\alpha)\cos(\beta) + \sin(\alpha)\sin(\beta)$             |  |

| Table 2.5 | Goniometrical | relations | used | in | this book |

|-----------|---------------|-----------|------|----|-----------|

|           |               |           |      |    |           |

$2\sin(\alpha)\sin(\beta) = -\cos(\alpha + \beta) + \cos(\alpha - \beta)$

$e^{\alpha}-e^{-\alpha}$

$2\sin(\alpha)\cos(\beta) = \sin(\alpha + \beta) + \sin(\alpha - \beta)$

$\sinh(\alpha) = \frac{e^{\dot{\alpha}} - e^{-\alpha}}{2}$

$sinh(\alpha)$

| $\tanh(\alpha) = \frac{\sinh(\alpha)}{\cosh(\alpha)} = \frac{e^{\alpha} - e^{\alpha}}{e^{\alpha} + e^{-\alpha}},$ | $\tanh(\alpha) = -j\tan(j\alpha)$                     |

|-------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|

| The argument of goniometric formulas is                                                                           | expressed in radians $(02\pi)$ , not in degrees [6–8] |

$2\cos(\alpha)\cos(\beta) = \cos(\alpha + \beta) + \cos(\alpha - \beta)$

$2\cos(\alpha)\sin(\beta) = \sin(\alpha + \beta) - \sin(\alpha - \beta)$

$\cosh(\alpha) = \frac{e^{\alpha} + e^{-\alpha}}{2}$

lists some mathematical properties of spheres and circles. Also the use of complex notation can help to visualize rotation (see Table 2.4).

Many events in nature have a cyclic and repetitive character. Sinusoidal waveforms describe these events, and Table 2.5 gives a number of regular goniometrical expressions.

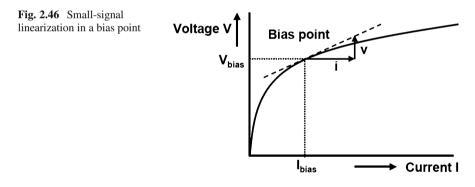

Derivatives of functions represent the way a function decreases or increases at every value of its variables. In electronics the derivative helps to understand the behavior of complex functions that are used in a small range of the main variables (Table 2.6).

Table 2.6

Standard manipulations for derivatives of functions [6–8]

| $\frac{\mathrm{d}u(v(t))}{\mathrm{d}t} = \frac{\mathrm{d}u(v)}{\mathrm{d}v}\frac{\mathrm{d}v(t)}{\mathrm{d}t}$                                                  | $\frac{\mathrm{d}u(at)}{\mathrm{d}t} = a\frac{\mathrm{d}u(t)}{\mathrm{d}t}$ |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|

| $\frac{\mathrm{d}}{\mathrm{d}t}(u(t)v(t)) = u(t)\frac{\mathrm{d}v(t)}{\mathrm{d}t} + v(t)\frac{\mathrm{d}u(t)}{\mathrm{d}t}$                                    | $\frac{\mathrm{d}}{\mathrm{d}t}u^n(t) = u^{n-1}(t)\frac{u(t)}{\mathrm{d}t}$ |

| $\frac{\mathrm{d}}{\mathrm{d}t}\left(\frac{u(t)}{v(t)}\right) = \frac{v(t)\frac{\mathrm{d}u(t)}{\mathrm{d}t} - u(t)\frac{\mathrm{d}v(t)}{\mathrm{d}t}}{v^2(t)}$ | $\frac{\mathrm{d}}{\mathrm{d}t}\ln(at) = \frac{a}{t}$                       |

| $\frac{\mathrm{d}}{\mathrm{d}t}at^n = ant^{n-1}  (n \neq 0)$                                                                                                    | $\frac{\mathrm{d}}{\mathrm{d}t}\mathrm{e}^{at} = a\mathrm{e}^{at}$          |

| $\frac{\mathrm{d}}{\mathrm{d}t}\sin(at) = a\cos(at)$                                                                                                            | $\frac{\mathrm{d}}{\mathrm{d}t}\cos(at) = -a\sin(at)$                       |

| $\frac{\mathrm{d}}{\mathrm{d}t}\arctan(at) = \frac{a}{1+a^2t^2}$                                                                                                |                                                                             |

Table 2.7

Standard manipulations for integrals of functions [6–8]

| $\int x^n dx = \frac{x^{n+1}}{n+1} + \text{constant}  (n \neq -1)$              | $\int_{-\infty}^{\infty} \frac{1}{x} dx = \ln(x) + \text{constant}$    |

|---------------------------------------------------------------------------------|------------------------------------------------------------------------|

| $\int \frac{1}{a^2 + x^2} dx = \frac{1}{a} \arctan(x/a) + \text{constant}$      | $\int_{x=0}^{\infty} \frac{1}{a^2 + x^2} \mathrm{d}x = \frac{\pi}{2a}$ |

| $\int_{-\infty}^{\infty} \sin(ax) dx = \frac{-1}{a} \cos(ax) + \text{constant}$ | $\int \cos(ax) dx = \frac{1}{a}\sin(ax) + \text{constant}$             |

| $\int_{x=-\infty} f(x)\delta(x-x_0)\mathrm{d}x = f(x_0)$                        |                                                                        |

| x                                                                               | 00                                                                     |

| $\operatorname{erf}(x) = \frac{2}{\sqrt{\pi}} \int_{t=0}^{t} e^{t^{-2}} dt$     | $\int_{t=-\infty}^{\infty} e^{t^{-2}} dt = \sqrt{\pi}$                 |

| $\int_{x=0}^{\infty} \frac{\sin(ax)}{x} dx = \frac{\pi}{2}  (a > 0)$            | $\int_{x=0}^{\infty} \frac{\sin(ax)}{x} dx = \frac{-\pi}{2}  (a < 0)0$ |

| $\int_{-\infty}^{\infty} \frac{\sin^2(ax)}{x^2} dx = \frac{a\pi}{2}$            | $\int_{-\infty}^{\infty} \frac{\sin^2(\pi x)}{(\pi x)^2} dx = 1$       |

| x=0<br>x=L                                                                      | <i>x</i> −−∞<br><i>u</i> − <i>I</i>                                    |

| x = L                                                                           | x = L                                                                  |

| $\int \sin(2\pi nx/L)\sin(2\pi mx/L)dx = 0,  \text{if } m \neq n$               | $\int \sin^2(2\pi nx/L) dx = 0.5  n,m: \text{ integer}$                |

| <u>x=0</u>                                                                      | x=0                                                                    |

Integration of functions is the main mathematical method to form summations over time, area, etc. Elementary manipulation of integrals of functions is given in Table 2.7.

In many applications the function f(x) is known; however, the behavior of this (perhaps) complicated function is required over only a small fraction of the entire range of x. If the function's behavior close to point x = a is needed, the derivative of the function gives the direction in which the function will change. By adding higher-order derivatives a series expansion is formed that is useful to represent a complicated function. A function as defined by its Taylor series looks like

Table 2.8 Taylor series expansions [6–8]

$$(1+a)^n \approx 1 + na + \frac{n(n-1)}{2!}a^2 + \dots, \quad |a| \ll 1 \qquad \frac{1}{1+a} \approx 1 - a - a^2 \dots \quad |a| \ll 1 \\ \sqrt{1+a} \approx 1 + 0.5a, \quad |a| \ll 1 \\ e^a \approx 1 + a + \frac{a^2}{2!} + \frac{a^3}{3!}, \quad |a| \ll 1 \qquad \ln(1+a) \approx a - \frac{a^2}{2} + \frac{a^3}{3}, \quad |a| \ll 1 \\ \frac{\sin(\alpha) \approx \alpha - \frac{\alpha^3}{3!} + \frac{\alpha^5}{5!} \quad \alpha \text{ in radians,} \quad |\alpha| \ll 1 \qquad \cos(\alpha) \approx 1 - \frac{\alpha^2}{2!} + \frac{\alpha^4}{4!} \quad |\alpha| \ll 1$$

$$f(x) = f(a) + \frac{(x-a)}{1!} \left. \frac{\mathrm{d}f(x)}{\mathrm{d}x} \right|_{x=a} + \frac{(x-a)^2}{2!} \left. \frac{\mathrm{d}^2 f(x)}{\mathrm{d}x^2} \right|_{x=a} + \frac{(x-a)^3}{3!} \left. \frac{\mathrm{d}^3 f(x)}{\mathrm{d}x^3} \right|_{x=a} + \dots$$

(2.1)

Table 2.8 gives some Taylor series expansions for regular functions.

The Taylor series expands a function at one moment in time. For static signals this representation is the basis for nonlinear analysis. The Volterra series is a method for including time-dependent effects:

$$\begin{split} f(x,t) &= \sum_{i=1}^{\infty} \frac{1}{i!} \int_{-\infty}^{\infty} \dots \int_{-\infty}^{\infty} g_i(\tau_1, \dots, \tau_i) x(t-\tau_1) \times \dots \times x(t-\tau_i) \mathrm{d}\tau_1 \dots \mathrm{d}\tau_i \\ &= g_0 + \frac{1}{1!} \int_{-\infty}^{\infty} g_1(\tau_1) x(t-\tau_1) \mathrm{d}\tau_1 + \frac{1}{2!} \int_{-\infty}^{\infty} \int_{-\infty}^{\infty} g_1(\tau_1) g_2(\tau_1, \tau_2) x(t-\tau_1) x(t-\tau_2) \mathrm{d}\tau_1 \mathrm{d}\tau_2 \\ &+ \frac{1}{3!} \int_{-\infty}^{\infty} \int_{-\infty}^{\infty} \int_{-\infty}^{\infty} g_1(\tau_1) g_2(\tau_1, \tau_2) g_3(\tau_1, \tau_2, \tau_3) x(t-\tau_1) x(t-\tau_2) x(t-\tau_3) \mathrm{d}\tau_1 \mathrm{d}\tau_2 \tau_3 \dots \end{split}$$

The first term in the Volterra series is the convolution function as in Eq. 2.149. Laplace and Fourier analogies of the Volterra series are useful to evaluate time-dependent distortion. Various techniques exist to estimate the coefficients  $g_i$ .

*Example 2.1.* Show that  $\sin(0.1\pi) * \cos(0.2\pi) = \sin(18^\circ) * \cos(36^\circ) = 0.25$

**Solution.** First multiply numerator and denominator with  $\sin(18^\circ)$ , then use twice  $\sin(\alpha)\cos(\alpha) = \sin(2\alpha)/2$  and on the result  $\sin(\alpha) = \cos\left(\frac{\pi}{2} - \alpha\right)$  to get